作者:李大虾

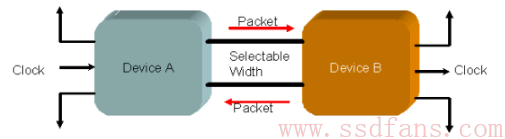

PCIe,2001年立春发芽,2002年出生,在Intel这颗大树下,必然不同凡响,就如主角降世。局部总线领域正在逐步取代PCI的地位,硬件上它继承了PCI的设计思路,软件上兼容PCI总线(但是硬件实现上完全不同,只是系统软件上看起来相同)。基于提高总线频率和带宽,高速串行总线逐渐替代了并行总线,这也是大势所趋。这时的限制在于传输介质,目前普遍是铜线路,传输极限是10Gbps。PCIe 3.0支持总线频率达到4GHz,信号频率可达到8GT/s(每个时钟周期传输2位),编码方案128b/130b,支持虚通路VC(Virtual Channel),每个虚通路有独自的缓冲区,分配给不同优先级的报文,更好的支持服务质量(QoS),数据传输方式与TCP/IP类似,包括事物层、数据链路层和物理层,区别在于PCIe用硬件逻辑而非软件实现协议栈。PCIe采用高速差分总线(要求“等长“、“等宽“、“贴近“、同层),点对点传输不被干扰,包括发送端(Tx)和接收端(Rx),因此共4根信号线,电气特性要求发送端接一个AC耦合电容。虽然PCIe链路是串行数据传输,但是芯片内部数据总线仍然是并行传输。

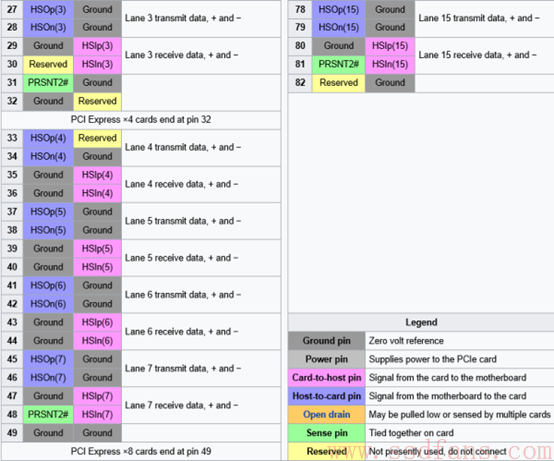

PCIe链路支持1(2*18=36pin)、2、4(2*32=64pin)、8(2*49=98pin)、12、16(2*82=164pin)、32个Lane,每个Lane的总线频率与PCIe版本有关,相当于位宽,比如:

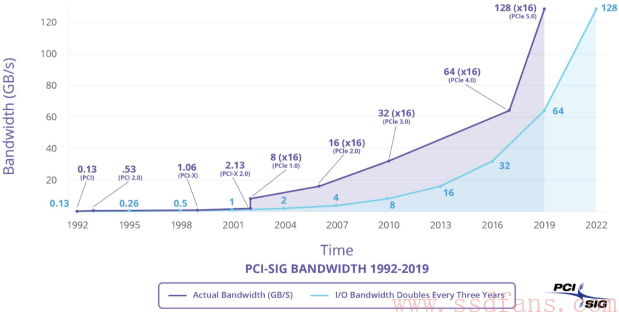

PCIe 1.x,总线频率1.25GHz,单Lane峰值2.5GT/s,8/10b编码

PCIe 2.x,总线频率2.50GHz,单Lane峰值5.0GT/s,8/10b编码

PCIe 3.x,总线频率4.00GHz,单Lane峰值8.0GT/s,128/130b编码

PCIe 4.0,总线频率8.00GHz,单Lane峰值16GT/s,128/130b编码

然而多见的是1 Lane链路。

8/10b编码:将连续的8位数据分成3位和5位两组,经过编码分别生成4位和6位两组,可保证DC平衡,连续的“1”或“0”不超过5位。

功耗情况如下:

x1卡:0.5A 12V (6W) 10W组合

x4卡:2.1A 12V (25W) 25W组合

x16卡:5.2A 12V (66W) 75W组合

PCIe信号:

Vcc和Vaux:额定电压3.3V,主要逻辑模块Vcc供电,电源管理和特殊寄存器(如Sticky Register)使用Vaux供电;Vcc可能被移除,降低功耗,而Vaux多数情况下不会,这样电源逻辑和特殊寄存器状态不会改变,缩短系统恢复时间。

PERST#:全局复位信号,复位方式有Cold Reset和Warm Reset。

REFCLK+和REFCLK-:与处理器系统同步,通常信号的传播速度接近光速,约6英寸/ns,不同PCIe插槽的REFCLK传输延时差约2.5ns,接入PCIe设备后可以用REFCLK也可以用独立时钟。Link Control Register的Common Clock Configuration位,为1表示设备与PCIe链路对端设备使用同相位参考时钟,为0则为异步的,默认值为0。

WAKE#:(可选信号)休眠状态,PCIe设备向处理器系统发出唤醒请求,重新启动Vcc,PERST#将进行复位操作,复位正常,WAKE#信号无效。

Beacon信号(差分信号D+和D-)也可实现唤醒。

SMCLK和SMDAT:与SMBus有关,便于PCIe设备与处理器系统交互。

JTAG:国际标准测试协议,由TRST#、TCK、TDI、TDO和TMS信号组成,实现在线编程ISP功能。

PRSNT1#和PRSNT2#:热插拨信号,在PCIe总线的Add-in卡中,PRSNT1#和 PRSNT2#直接相连,处理器主板系统中,PRSNT1#接地,PRSNT2#通过上拉电阻接为高,插入时PRSNT2#为低来判断热插拨。该信号pin为短针结构。

硬件协议:

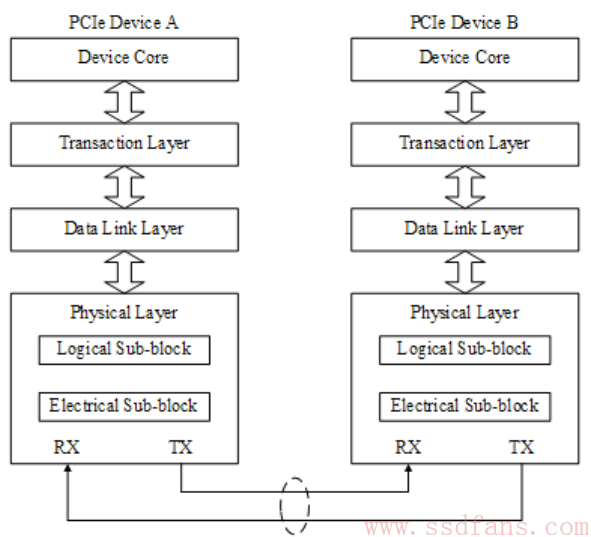

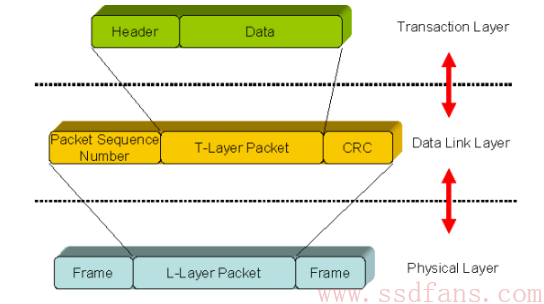

数据包传输,经历事物层、数据链路层和物理层 Device Core(核心层):产生数据报文

Device Core(核心层):产生数据报文

Transaction Layer(事务层):接收/发送核心层的数据报文,封装/解封事务层数据包(TLP),转发/接收到数据链路层。包括流量控制、报文乱序管理等。

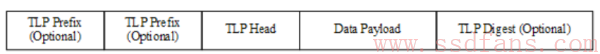

TLP的一般格式如下: TLP Prefix可以是一个或多个;TLP Head包含总线事务类型、路由信息等一系列信息;Data Palyload数据大小可变,0~1024DWord,比如存储器读请求、配置和IO写完成TLP就不需要Payload;TLP Digest,可选项,是否需要由TLP Head决定。

TLP Prefix可以是一个或多个;TLP Head包含总线事务类型、路由信息等一系列信息;Data Palyload数据大小可变,0~1024DWord,比如存储器读请求、配置和IO写完成TLP就不需要Payload;TLP Digest,可选项,是否需要由TLP Head决定。

TLP报文格式类型有:

存储器读请求TLP和读完成TLP、存储器写请求TLP、原子操作请求和完成报文、I/O读写请求TLP和读写完成TLP、配置读写请求TLP和配置读写完成TLP、消息报文。

消息报文类型包括:INTx中断消息报文(INTx Interrupt Signaling)、电源管理消息报文(Power Management)、错误消息报文(Error Signaling)、锁定事务消息报文(Locked Transaction Support)、插槽电源限制消息报文(Slot Power Limit Support)、厂商自定义消息报文(Vendor-Defined Messages)。

Data Link Layer(数据链路层):封装或解封数据链路层数据包DLLP,包含Sequence Number前缀、CRC后缀等,并使用ACK/NACK握手协议保证报文可靠完整传输。

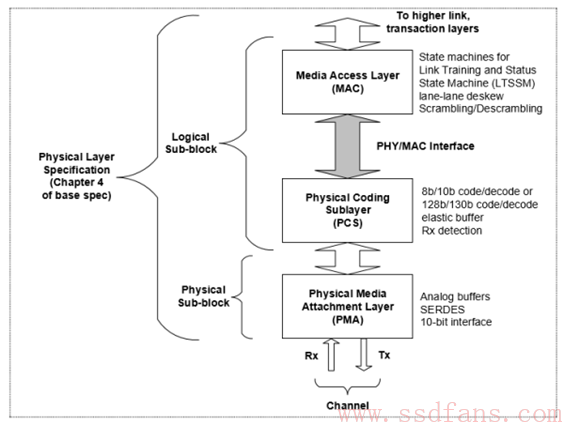

Physical Layer(物理层):传输数据序列(PLP),物理层包含逻辑和电气子模块,逻辑的进一步被划分为MAC和PCS,电气的包含单向LVDS(低电压差分信号)对。

Physical Layer(物理层):传输数据序列(PLP),物理层包含逻辑和电气子模块,逻辑的进一步被划分为MAC和PCS,电气的包含单向LVDS(低电压差分信号)对。

Intel的物理层进一步划分如下: