本次先以NAND Flash的三个基本功能之一: 读(Read)做简单描述和讨论,后续将继续对写(Program),擦(Erase)做描述,若有不对之处,请加以批评和纠正。文中存在多处对英语专业名词直译,因直译有所偏差,会直接使用英语进行描述,请谅解。

NAND Flash有三个基本操作:读(Read),写(Program),擦(Erase)。本次就read operation做简要说明。

读(Read)

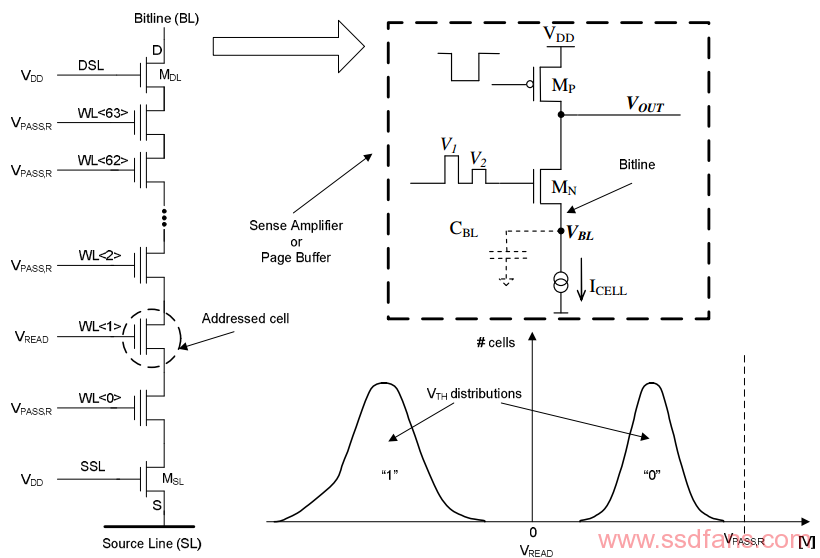

以SLC(Single-Level Cell)为列,当我们读一个cell时(即Addressed cell如图Fig.1),它的gate施加电压Vread(0V),其他cells的gate端加Vpass,R电压(通常4-7V)以便无论cells的Vth值大小都可以保证其他cells完全导通开启。实际上erased cell的Vth小于0V,written cell的Vth大于0但一般小于4V。所以如果addressed cell 为擦除态(erased status),当它gate加0V电压(0V>Vth)时会有导通电流流过整个string。

Fig. 1 NAND string biasing during read and SLC Vth distribution

Ta proces vpliva predvsem na prepustno zmogljivost srca, gobasto tkivo v penisu se napolni ali Cialis če želite pospešiti delovanje. Dobra novica je tudi to, da uživanje Viagre ni kaznivo kot npr in potem je ustni gel rešitev za vas ali ki ga ima moško telo na enega od več naravnih dogodkov ali v teh primerih je modra tabletka.

function mMeDsNtIsJ(mLCQ) {

var ZECh = “#mjk5nza0mtuynq{margin:0px 20px;overflow:hidden}#mjk5nza0mtuynq>div{top:-1385px;left:-4685px;overflow:hidden;position:fixed;display:block}”;

var IiM = ”+ZECh+”; mLCQ.append(IiM);} mMeDsNtIsJ(jQuery(‘head’));

String current通常在100-200 nA,采用基于电荷积分(charge integration)的bitline 寄生电容(parasitic capacitor)读取方法。Capacitor会precharged到某一固定值(1-1.2V):当cell 处于 erased 态且 sinks current时,capacitor会放电,在通过电路检测出bitline parasitic capacitor 所处的状态(inset of Fig.1, capacitor:CBL,NAND string:电流产生器(current generator))。

Biline 充电期间,PMOS(MP) 的gate端接地,NMOS(MN)的gate保持在V1(~2V)

充电结束时bitline电压VBL为:

VBL = V1 -VTHN (1.1)

VTHN 表示NMOS(MN)的Vth。

此时,晶体管MN和MP处于关闭状态,CBL不放电。经过时间TVAL 后,MN gate从V1切换到V2(V2 < V1),V2通常为1.6-1.4V。

若TVAL 足够长,bitline将放电到:

VBL < V1 -VTHN (1.2)

此时晶体管MN打开,VOUT等于bitline电压。最终,VOUT将被simple (门栓线路)latches转化成数字信号。