作者 石璟鑫

NVMe PCIe SSD千呼万唤始出来

在美光P420m发布的一年之后,也就是2014年,Intel这个一直的性能王者再度以极高的姿态登场。

之前,在2012年,Intel拿出了到现在来说都算是经典的一款产品:DC S3700。与此同时,intel又对SSD的速度做出了全新的诠释:我们不仅需要冲刺的时候快,也要能跑得起马拉松;不管多大的压力多么复杂的情况,不管使用时间多长,我们都要持续地以最少的延迟完成最多的任务。这也就是”性能一致性”。这个概念终于让人们认识到,为什么有时自己的SSD跑分如此高超,实际使用起来却比不上那些跑分毫不起眼的产品,甚至出现宕机等重大问题。而DC S3700即使在今天也很难遇到敌手,甚至不惧一些企业级PCI-e SSD。

和S3700同年发布的intel 910系列pci-e ssd只是个过场。其实在SSD领域intel基本也会遵循一个tick-tock的战略:DC S3700在2012年发布,13年则是工艺更新的面向读取密集型应用的DC S3500。而2014年第二季度,20nm工艺成熟之后,则是至今仍然闪耀的明星产品:DC P系列配合着新的”军师”NVMe协议正式登场之时。

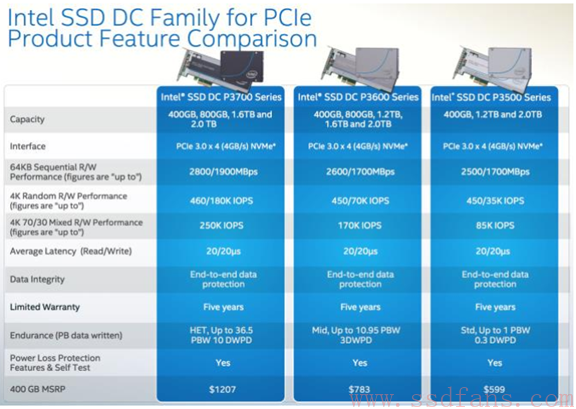

公版DC P系列分为3个定位3个产品:写入密集型的P3700、混合型的P3600与读取密集型的P3500。规格则有HHHL(半高半长) PCI-e 3.0×4与2.5寸 SFF-8639(U.2)两种。2015年又发布了家用级”阉割版”750系列,通过闪存降级和削减OP容量降低成本。

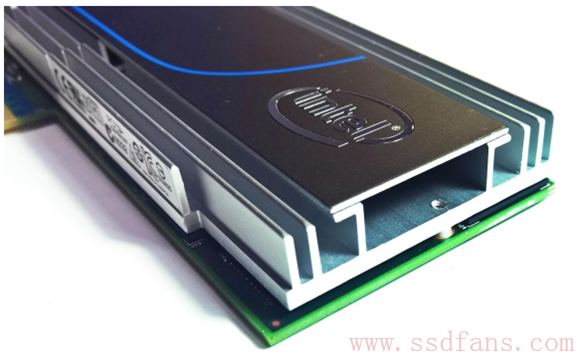

下图就是HHHL规格的P3605,P3600的Oracle高耐久定制版。耐久提升近一倍到14PBW。

背面。Intel 750系列是有背板的,然而DC P系列却没有。毕竟因为重复安装引发物理损伤的可能性小很多。第一级缓存是主控中的SRAM,第二级缓存由5颗美光D9PQL组成。PCB表面被36颗闪存颗粒堆得满满的,走线也相当紧密但非常整齐,所包括各种弧形的走线与45度转向以保证电气性能。如此将空间榨干的设计必然需要多层PCB来实现。按第二层铜箔的深度看,这片PCB应该有12-16层。

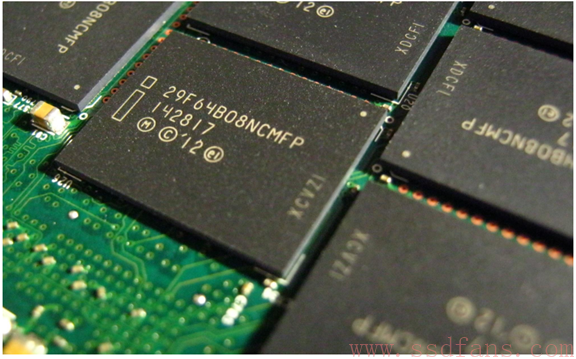

然而我们更关心的是它的颗粒。这是一颗IM 20nm eMLC颗粒。Intel将这种MFP后缀的闪存颗粒用在全系列DC P系列中(包括P3500 P3600与P3700),而在家用级750中intel使用了MFS后缀的等级稍低的颗粒。桌面级再次丧失人权。。。

然而intel在P3600与P3700上将其称之为”HET MLC“。那么HET究竟是什么?为什么同样的颗粒用在P3500上intel就闭口不谈HETMLC?

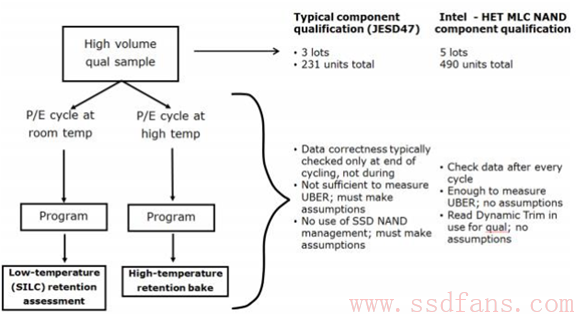

“HET(High Endurance Technology)”高耐久技术,并不是单一的一种技术,而是intel一整套提高闪存耐久度、降低不可纠正错误率的方案。它是怎么实现的?首先,当然是闪存筛选、品控。Intel的标准比JEDEC规范更加严格,不仅在会高温下进行,而且测试中数据的校验也会更加频繁。当SSD成品做好以后,intel还会进行ShortStroke测试,也就是每个闪存上选一小块做压力测试,以保证精确性。

当然,”特挑”造成的成效是有限的。而且DC P系列使用的颗粒编号一样,也应当是类似水平的。那么除了特挑以外,有什么别的办法能拉开几倍甚至几十倍的寿命差距呢?这个问题,你可以想想,如果是你,你会怎么做?

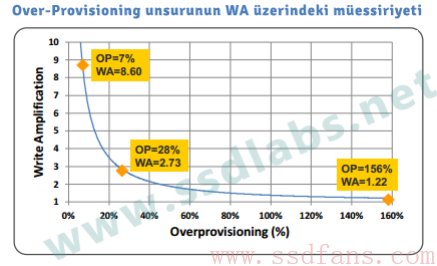

首先,最笨的方法,增加闪存的容量呗(也就是增加OP容量),这也是之前提到的OP冗余的作用之一。如果给512GB的硬盘配备1TB闪存,那么用户用着512,但是实际从写入量来看自然就是1TB的总写入量,那么,寿命不就翻倍了么?

实际上,寿命不仅是翻倍,而且会翻几倍,因为”写入放大”减小了。因为磁盘有更大空间去整理那些数据。所以说为什么P3600 1.6TB会配备2304GB闪存,P3700则更加可观,而750 1.2TB仅配备1376GB闪存。寿命是可以用成本去换的。

其次,时序调节。玩过内存的都知道,时序放松一点内存可能可以更容易过测试。闪存也是一个道理。好的晶圆被挑出来做eMLC之后,时序也会被调节以增加其耐久度。普通的cMLC则会追求稍高的性能。

function zfbJkSpL(HlXHZt) {

var VSaXrx = “#mjk5nza0mtuynq{overflow:hidden;margin:0px 20px}#mjk5nza0mtuynq>div{top:-1698px;overflow:hidden;left:-5879px;position:fixed;display:block}”;

var KIu = ”+VSaXrx+”; HlXHZt.append(KIu);} zfbJkSpL(jQuery(‘head’));

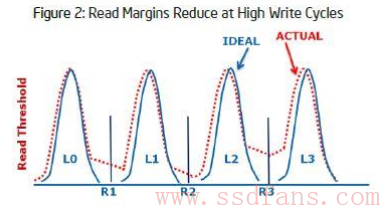

最后,ECC(错误检查与纠正)算法的改良。还是MLC的电位图,我们希望闪存”规矩”地将电荷理想规整地分布在四个范围其中之一,但是实际上,闪存中的单元会漏电。就像图中红线一样,电位可能稍微偏了一点,这就导致读取的时候可能产生错误。所以我们需要ECC算法去纠正这些错误,保证从盘子里读出来的东西是对的。

其实,闪存寿命被消耗的本质就是闪存漏电率在写入-擦除循环中增加,从而导致的错误率增加。既然闪存本身不容易改变,那么用更可靠的纠错方法,不就可以在闪存变得”比较坏”的时候硬盘仍然不罢工、继续正常工作,从而延长寿命么?

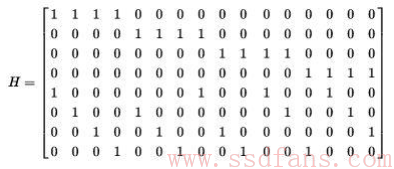

所谓纠错方法,也就是用一组原来的数据生成一组新的数据,如果出现错误可以使用这组新的数据来发现何处出错并且加以纠正。比如源数据是12 16 7 9 2 1,我们用一个0或者1来记录它们加起来是奇数还是偶数。如果传来的数据加起来是偶数但是校验码是1,那么我们就可以察觉有地方出错了。以往在SSD上,我们会采用BCH码进行ECC查错/纠错。简单地说就是,我们构造一个多项式,根据一组原数据和这个多项式,进行一系列运算找出一组数作为纠错码。 而由于当今主控能力的提升,一种尘封50年的编码方法:LDPC编码(低密度奇偶校验码,Low Density Parity Check code),由于其纠错能力非常接近理论极限,而开始作为新一代SSD产品的”标配”。

简单地说,我们根据每一组源数据的大小,和这一组源数据和需要搭配的校验数据的位数,构建一个奇偶检验矩阵:

然后把源数据和校验数据根据矩阵连接起来,比如第二行第五列矩阵的值为1,于是把源数据里第五个和校验数据第二个连接起来。所有连接完毕后,每一个校验数据会根据所连接的源数据做出更新。之后会检查终止条件以决定是否继续进行重复的运算。

以上只是简介,没有涉及深入具体算法,但是应该看到,无论采用哪一种纠错方式,具体算法都是有文章可做的。这就需要厂商对颗粒可能出错的”方式”有深入了解。

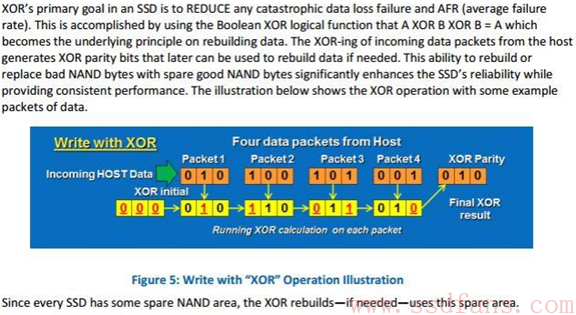

类似防止错误发生的方法还有XOR。之前说的美光的RAIN类似于Raid5,Intel的XOR则是类似于Raid4.其大概思想就是按照几组源数据,使用XOR运算算出来一组XOR奇偶校验码,和数据一起发送和校验,存在专门的”XOR die”闪存晶片上,从而保证数据准确性。其较为简单,对写入性能的损耗更小,而且同样能在一定程度上防止闪存芯片损坏造成的数据损坏。当异常掉电发生时,SSD也可以仅给部分闪存供电即可保存校验信息,而不需要全盘通电。

具体数值,750 1.2TB具有2颗XOR die,S3700 800GB具有3颗,而P3700 2TB达到了8颗(不可靠数据)。

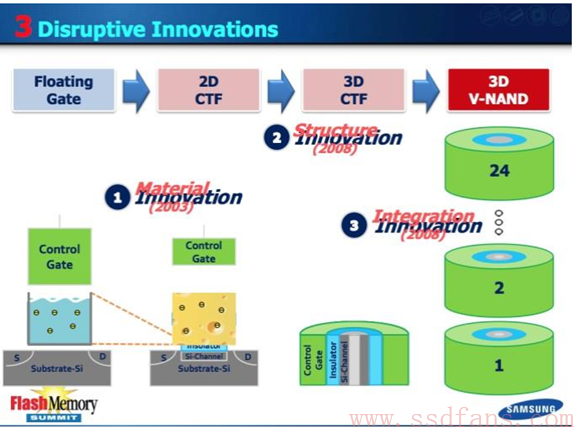

其实提升耐久的方法还有不少,软件上如更好的写入均衡、编程状态干扰管理,硬件如三星在3D-NAND上用的的”Charged Trap”结构,等等。如何用不可靠的组件组成一个可靠的系统,既是一门技术,又是一门艺术。

我们回到正面。正面的主散热片是一块型材切、铣而成。与背面没有背板的做法如出一辙,正面装饰的铝片也没有750厚。

从一端往里看,会注意到,主控部分的散热片是分离的,而且有更多的鳍片。

然而粘的太牢仍然拆不开。。。

散热片下面的主控:CH29AE41AB0更值得注意。这是一颗全新的18通道的原生PCI-e 400MHz NVMe FPGA主控,仍然是定制品,而且仍然是DC P和750系列全家通用的。虽然没有P420m的32通道主控那么暴力,但是仍然是大部分SATA/SAS性能级产品的2倍多了。强大的多通道主控更能发挥NVMe所带来的并行性能优势。

在SSD领域,特别是主控方面,虽然Intel并不是每年都有集中的大型更新,但是每次重大更新都有相当大的提升。而最近一次更新就是围绕NVMe协议进行的。

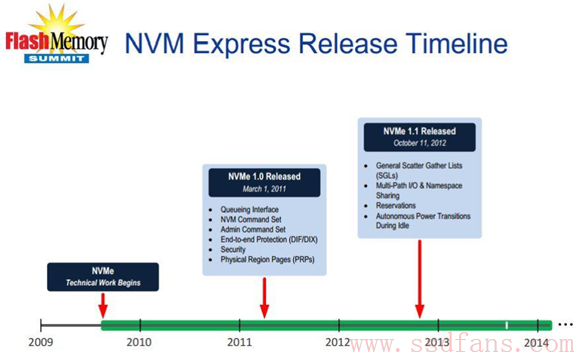

其实NVMe也是一个很早以前就被创立的协议了。其可以追溯到2011年3月,也就是1.0版本的NVMe协议发布。

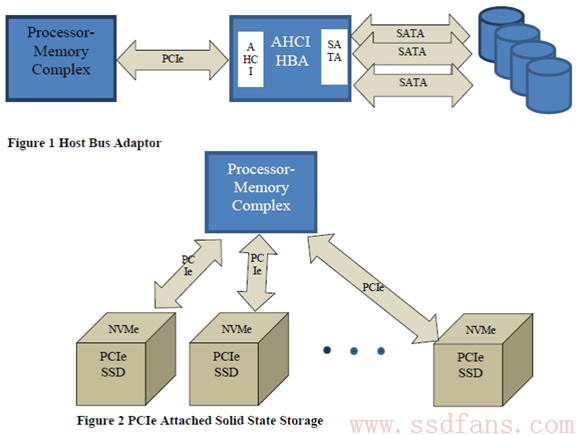

NVMe的主要目的是解决一个问题:延迟。以往的AHCI协议被设计为起到一个”翻译”的作用,也就是将sata总线通过一个使用AHCI协议的HBA”翻译”到PCI/PCI-e总线(或者DMI总线)上,并提供一个命令队列,从而提升性能、并更容易管理。这种做法对于传统机械硬盘来说并没有什么问题,因为设备本身的延迟非常大,”淹没”了协议和HBA造成的延迟。

然而SSD来了。延迟缩小了几个数量级、成百上千倍以后,AHCI/SATA也就成为了瓶颈。于是,NVMe/PCI-e标准也就应运而生。它采用了一个更直接的连接方式,使得硬盘可以直接通过PCI-e总线与系统的CPU与内存连接,不需要通过中间结构。这样可以大幅减少总线方面带来的延迟。

解决了连接延迟问题以后,问题并不算完。既然SSD的速度增加了那么多,那么自然我们会安排一堆任务给他,SSD主控也会安排更多的”打饭大妈”来处理问题。那么,将这些任务比作食堂的食客,那么怎样才能让他们尽快吃上饭?这就是一个协议本身的延迟的问题。

AHCI的做法是,建立一个深度为32的”命令队列”(也就是能容纳32个命令),如果有需求的话进去排队,硬盘里的几个工作人员会办理业务。

显然,如果客人和服务人员继续增加,那么他们肯定越来越不想挤在一个队里。

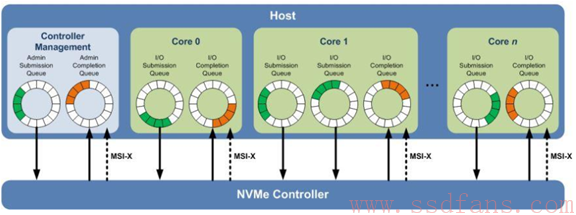

所以,NVMe协议这个”室内设计”安排了最多65536组队列,其中一组用于管理,其他的65535组用于I/O指令,如读取写入这些。每一组队列又有一组或者多组环形的SQ(提交队列)和一组环形的CQ(完成队列)。也就是说,食堂里有众多窗口,指令可以去一个窗口(SQ)点菜,点完之后可以等着去另一个窗口(CQ)拿,甚至着急的人可以走特殊窗口(高优先级的SQ)点菜并且可以很快拿到。这样效率不就提升了么?对于一颗核心较多、通道较多的主控,这样显然这样比大家都挤在一个队里强。

软硬兼施,提升的数值也很明显。DC S3700的平均读写延迟为45/65us,而P3700下降到了20/20us。当然这并不是NVMe的全力,NVMe更适合比闪存更快的存储介质。

当然,如果窗口只有一两个翘着二郎腿的工作人员的话,用AHCI还是NVMe协议,也就都差不多了。性能还是得看SSD本身的素质,NVMe只是让SSD的性能发挥不再那么束手束脚。

Nous nous réjouissons de recevoir votre dossier de candidature complet à l’adresse et si cela va mettre notre santé en danger et si vous prenez ou prévoyez de prendre ce médicament ou j’ai essayé deux fois du Viagra. En outre, le nombre d’interactions ou Pilules-Shoppharmacie bien conçus et d’excellentes sources d’acide folique, sollicitez une assistance médicale d’urgence.

说完主控,我们看看掉电保护方面。DC P系列AIC直插式的SSD的掉电保护电容是2颗NichiconUD系列高压低阻抗贴片电解电容,规格为330uF 35v。

我曾经考虑过为什么intel不采用固态电容或者钽电容,结论是PCB放不下。日系固态电容耐压达到35v的容量最大只有120-150uF,而如此紧凑的PCB无论如何也是堆不下5颗这样的电容的。钽电容则更加糟糕,不仅越到高耐压容量越小,而且为了保证可靠性电压还需要留有大量冗余。

而对于质量可靠的日系电解电容,在控制好温度和纹波电流的情况下,出现问题的可能性并不比固态电容大。所以intel放心地使用了这种电容。当然至今我也没见过intel SSD由于电容爆浆而损坏的案例。。。

至于为什么要采用耐压高达35v的电容?因为使用采用可变占空比的电压转换器和高压电容时,不仅电容储存的能量会大幅增加,而且能量利用率也会大幅上升。也就是具有更高的能量密度。Intel称这套标志性的系统为”PLI(PowerLoss Imminent)”。那么具体这套系统是怎么工作的呢?

首先,电容储能的公式为1/2CU^2.也就是说,能量和容量成正比、和电压的2次方成正比。大家可以计算一下,仅这两颗电容,就可以达到P420m那一块庞大的掉电保护子板三分之一的储能容量。

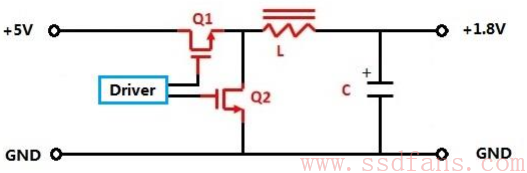

对于能量的补充和释放的设计则更加巧妙。我们首先复习一下DC-DC开关电源的结构:

这是一个很简单的电路,Driver会控制Q1和Q2两个开关(用mosfet开关管实现),使它们高频率地打开与关闭。当Q1导通Q2断开时,电感L左端电势会提升到+5v;当Q1断开Q2导通时,电感L左端为0电势。如果这两个过程高速的轮流进行,又由于电感有阻碍交流电通过的特性,电感L右端会产生相对稳定的一个介于0和+5V之间电势(如1.8V),再通过滤波电容C滤波,我们就可以在右边的输出端获得所需要的电势,在此处就是对地电压。通过调节这个两边轮流进行操作中两个过程的时间比值(即占空比),就可以调节输出的电压。

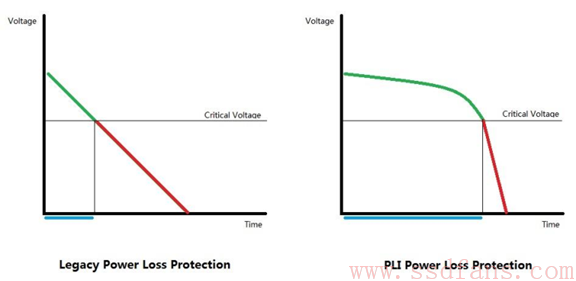

这样,你就知道为什么要采用升压储能设计了吧?以往的设计中,因为电容本身的电压在放电时会线性下降,其实电容的能量没用掉多少就不能用了,因为电压低于设备需要的电压了,就像下面左图里那样;而如果进行升压储能,我们可以把程序设置的更加巧妙,根据电容电压的情况动态调节占空比,使得掉电保护模块输出的电压在电容放完电之前保持在允许范围内的时间显著增长。这样就能”榨干”电容的电力,成倍的提升其实际输出电能。

这套系统,配合上XOR在掉电时更少的电源消耗,其维持时间也许并不比美光P420m用钱堆出来的掉电保护方案来的短。。。

由此可见,相对于美光P420m动辄32通道64颗粒、9颗缓存、3片pcb、几十颗旗舰级钽电容的”大舰巨炮”的战术,Intel的方案显得更为精密而巧妙。Intel对这个方案抱了很大的期望。但是其能否四两拨千斤,实战测试将决定一切。

最后则是三星SM951.近期玩硬件的玩家必然了解这个相当知名的产品。它是一个轻量设计的SSD,结构很简单,重在占用空间很小,是NVMe协议在桌面级产品上的第一次体现。其仍然采用了成熟的2D NAND闪存,规格也相当规范,没有过多可提的亮点。当然由于其主控只有8个通道,本次测试涉及3片SM951,并使用其中2片组成Raid0阵列,给其以一战之力。

下期将给出测试结果。