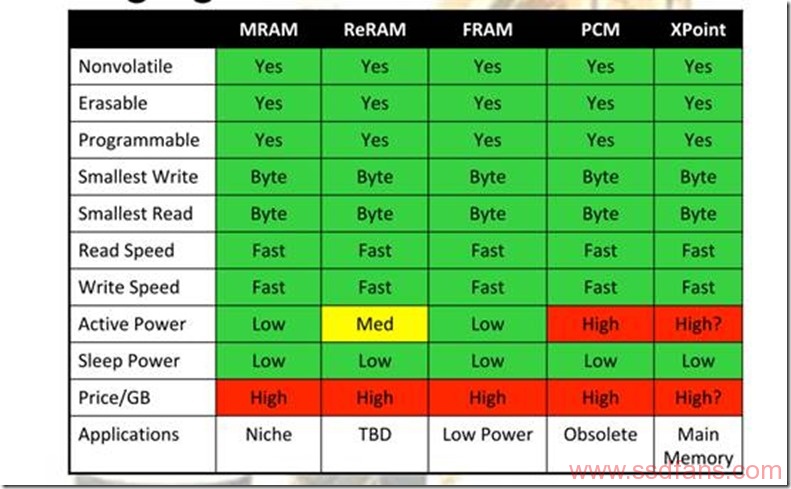

研究机构IMEC已经发表了一篇论文,该研究表明,在5nm节点上, STT-MRAM与SRAM相比可以为缓存提供节能效果。这种优势比非易失性和较小的空间占用更好。

本周,半导体研究的核心商业合作伙伴IMEC在加利福尼亚州旧金山举行的国际电子器件会议(IEDM)上发表了大量论文。

在关于5nm嵌入式MRAM的论文中,IMEC使用经过硅验证的pMTJ紧凑模型进行了设计分析,该模型与5nm节点兼容。对于读写操作,pMTJ称访问延迟分别小于2.5ns和7.1ns。分析表明,STT-MRAM满足了高性能计算中一级到三级缓存的众多要求,并且读写性能显著高于SRAM。它满足了超过100MHz的时钟频率[……]