本文旨在为从事NAND characterization的工程师提供业内一些成熟的测试经验。在构建高质量存储部件(如SSD)时,NAND characterization的挑战在于对实验的正确设计以及对获得结果的正确解释。本文将讨论几种技术以改进整体NAND characterization过程。

为什么需要Characterization

现代大容量存储使用固态组件,主要是NAND闪存。NAND远比使用其它非易失性存储器技术构建的组件更具成本效益。因此,即使它们存在固有的出现故障的风险,它们的应用也是不可或缺的。

大多数NAND故障的起因是由于构建高密度、低成本存储器所需的极具挑战性和快速发展的技术,较小的尺寸形状意味着较小的存储cell单元彼此更加接近,这大大增加了存储cell单元干扰的可能性。3D体系架构产生的阵列(array)在每一层的cell都有一定的特性差异,将多个位(bit)压缩到同一个存储cell(SLC – > MLC – > TLC – > QLC)会降低存储在单个cell中的不同状态之间的读取余量,这会增加噪声和温度灵敏度并降低数据保持(retention)的余量。所有上述这些 NAND技术的问题都会影响NAND的特性,包括耐用性,数据保持,以及自我恢复能力等。

部件级的最终产品,如SSD,需要读/写快速并且可靠。由于内置的NAND无法匹配这些要求,控制器(SSD控制器)必须补偿NAND可能出现的故障,例如使用ECC,读重试,损耗均衡,坏块管理等几种技术。这通常通过控制器固件中实现的专用算法来完成。

编写有效的算法需要深入了解NAND故障模式(补偿什么?如何补偿?)。不幸的是,这不是一件容易的事,因为每个新NAND或NAND家族系列产品都有不同的故障特征,这些特性也取决于使用模式。NAND供应商的产品技术单页仅提供一般可靠性相关信息,SSD开发人员的任务是找到属于他们自己SSD应用的特定的最佳参数。

这就是需要在应用层面进行NAND characterization必不可少的原因。空谈“正确的设计和执行提供有效的测试结果”是没有什么实质意义的,测试必须依据一定的流程和规范,同时使用专用NAND测试工具才能达成真正有效的测试结果。否则的话,很可能出现在characterization期间测量的NAND行为与在其被应用于SSD中时的性能完全不同的风险。

Characterization 流程

NAND characterization必须以“用户模式”(User Mode)执行,因为NAND制造商不会公开其“测试模式”(Test Mode)。 测试模式提供更高的可见性,如直接在存储cell单元级别测量阈值电压和电流,构造(topologic)加压,构造位图(bitmapping)……另一方面,用户模式characterization更接近最终应用,因此细致的测试设计并执行一系列实验才可以提供非常有意义的数据用于分析。

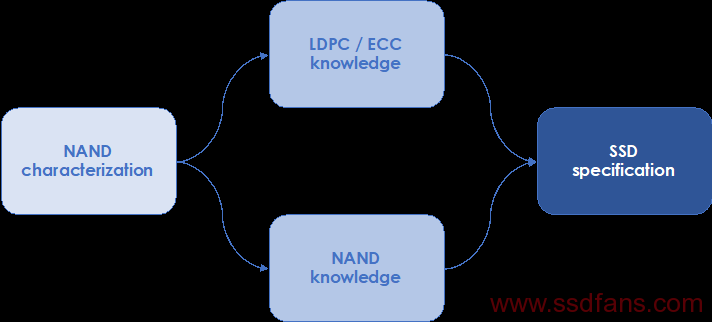

characterization流程的高级视图如图1所示。Characterization将增强用户对于NAND器件的理解,其特性也决定了未来SSD Spec规格以及产品开发过程中最佳LDPC / ECC算法实现。

Figure 1: Top Level Characterization Flow

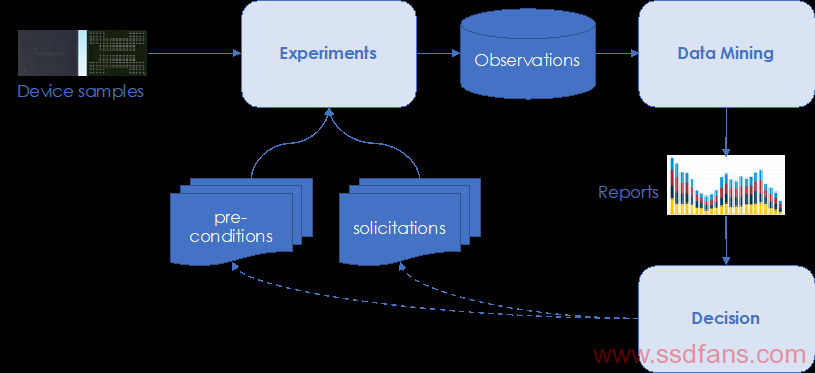

NAND characterization可以如图2所示建模。关键要素是“实验”设计。实验需要在精心挑选的一组NAND上执行,并进行适当的预处理。对这些NAND发出测试请求,并且执行测量以生成大量可供“观测”的数据。然后数据挖掘技术将被应用于从这些数据中提取信息,生成人类大脑可以理解的数据,从而产生可以带给测试工程师生成下一轮测试的新的一系列请求和预处理操作的决策信息。

Figure 2 Experiments in the Characterization Flow

实验规范

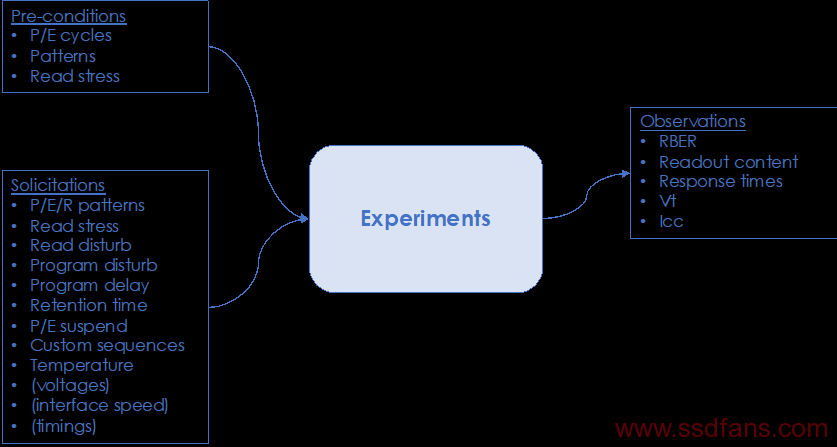

如前所述,用户使用基于ONFI标准的NAND通信接口以“用户模式”进行实验。 其它元素包括温度,时序和电压。 图3提供了概述,接下来的部分将描述细节。

Figure 3 Experiment specification

NAND Flash样本

Characterization通常在从NAND供应商获取的有限样本上执行。有些新的、早期的NAND可能还是一些工程样品,这往往会增加NAND测试出现问题的可能性。

为了获得合理的测试结果,对于NAND Flash样本的选择非常重要但其重要性经常被低估。

样本必须采用相同的技术(这个原因相当明显)制造,最好来自同一生产批次。

由于实验通常在一个容量较大的NAND Flash的一小块区域(单个block或几十个block)上进行,因此待测试block的构造位置必须是一样的,以避免内部布局(layout)对观测结果的影响。

在wordline或stack层面测试时,构造位置将更为重要。

预处理(Pre-condition)

预处理使待测NAND (DUT – device under Test) – 或其中的一部分 – 进入实验状态。 通常,实验的目标是设置不同的预处理条件,然后进行反复相同的测试。

最常用的预处理是实验之前在NAND Flash上执行的循环次数。由于磨损(wear-out)效应具有很大的影响,因此必须通过编程/擦除周期精确地预处理待测目标区域。

用于编程/擦除(P/E)循环的pattern也可能对测试结果产生影响。可以设置伪随机或构造相关模式的pattern。

另一种不太常用的预处理条件是大压力读操作。

测试请求

P / E / R模式:为了创建与最终SSD应用类似的条件,通常使用伪随机模式pattern进行测试。随机pattern的质量非常重要,pattern的生成为测试工具带来了挑战 – 其pattern生成的计算速度要求非常快速,否则将影响信号序列的时序。

读取压力:在压力区域上进行读取操作,通过施加读取电压来请求存储cell。短时间内的高读取数量会增加实验吞吐量,因此无需验证内容甚至直接从page缓冲区中读取内容。

读干扰:读取操作不作用于要加压的区域,而是作用于邻近区域。该操作应与压力区域上的读造作采用同等压力。

程序干扰:在邻居区域(通常是wordline)上进行测试操作。Programming所需的高电压可能会影响受干扰cell的状态。

程序延迟:Programming操作之间的时间对于理解驻留效应(dwell effect)至关重要,因此必须小心控制。

数据保持时间:Programming和读取之间的时间。必须对其进行控制,以便了解数据随时间的退化情况。还可以检测自恢复现象。

P/E暂停:暂停操作触发一系列的多种内部现象,因此实验必须涵盖这方面测试。测试的时机是至关重要的,因为必须在测试操作序列的特定时刻控制挂起操作。

自定义序列:可能需要试验非标准,供应商特定命令或命令序列的效果。

温度:这是影响可靠性的关键因素。它对programming质量,数据保持和干扰/压力测试敏感性都有很大影响,所以,必须精确控制温度。有些方法能够测量片上温度,但通常一个良好的基于package level的温度调节(一般是加温)将更适合该项测试。

电压:接口(interface)和内核(core)电压也可能对实验结果产生轻微影响。

接口速度:高速接口有助于快速进行实验。另一方面,由于信号完整性而不是cell array问题导致的错误概率会增加,因此必须精确地进行测试的设计和验证。目前已经有相关研究在讨论接口速度对cell array可靠性的影响。

信号时序:该时序通常不在实验的范围。

观测结果

良好观测的关键是将环境引入的问题与实验所针对的源自NAND array的问题分离开来。

RBER: Raw Bit Error Rate是指在没有任何纠错的情况下,每个block, page或者chunk失败的比特数。与pattern生成一样,高速运算对于减少实验开销和获得更精确的时序非常重要。

响应时间:闪存操作(擦除/编程/读取)响应时间提供了有关当前测试单元(cell)的状态信息。该时间需要在RDY / BSY信号上以足够的分辨率(<100ns)进行测量。

Vt:该挑战是在用户模式下获得Vt分布,以便查看分布的变化或扩大。而原厂的测试模式允许向存储单元(cell)提供外部参考并连续测量每个单元的阈值电压。受限于用户模式,可以使用读取重试命令获得足够精确的Vt分布。

Icc:功耗提供有关测试操作执行和NAND array状态的信息。由于精确的动态测量对测试工具提出了更多挑战,因此其使用相当有限。

数据分析

实验产生大量数据,必须转化为信息才有价值。 数据记录文件通常存储在数据库中,数据库是后处理的数据来源。由于后处理算法取决于实验,因此这些算法的开发也是实验的一部分。

输出通常是2D或3D图表,分布以及偶尔的构造或半构造位图(bitmap)。

测试工具

没有好的工具,实验就无法有效执行。 针对工具的关键要求如下:

可以同时执行多个独立实验。这意味着测试程序和测试参数应该是每个待测NAND都可以设置为不同。由于温度也是测试流程的一部分,温度需要在实验过程中进行调整变化,因此针对单个NAND的独立温度控制至关重要。

不同NAND的测试应允许异步运行,这样在一台设备上可以允许随时加入NAND进行测试,因为不同socket的NAND的测试是完全独立的,这也非常有利于长期测试。

系统开销也是保持测试时间较短的重要因素。

测试工具需要使用业内成熟的产品,因为系统引发的错误可能掩盖真实的观测结果,从而导致无意义的测试结果。

对于非专业用户,实验管理需要简单明了。为了不失灵活性,最好是同时拥有易于使用的操作员管理界面和灵活的工程界面。

数据收集必须自动化,以避免测试结果在分析时面临可能数据缺失的风险。

Tamas Kerekes是NplusT的总裁兼首席执行官,NplusT是一家位于意大利的公司,为非易失性存储器提供测试和characterization设备和服务以及数据分析软件工具。Tamas在半导体和大容量存储行业拥有强大的技术背景和专业知识。在加入NplusT之前,Tamas在为半导体和电子行业建立测试和可靠性测试设备的公司中担任过多个管理职位。他出生于匈牙利,1982年获得布达佩斯技术与经济学院学位。

Tamas计划在2019年3月25日一周在中国就NAND测试做技术交流,感兴趣的朋友可以提前预约时间面对面交流。