当我们分析AMD的第一代EPYC时,其最大的缺点之一就是太复杂。AMD通过启用四个8核硅芯片,并将每个芯片连接到两个存储通道,构建了其32核Naples处理器,这就导致了一个不均匀的存储结构(NUMA)。由于这种“四NUMA”架构,许多应用程序中都有很多NUMA平衡问题。几乎在每一个操作系统中都存在这种问题,在某些情况下,我们看到报告称系统管理员必须做大量的优化工作,才能从EPYC 7001系列中获得最佳性能。

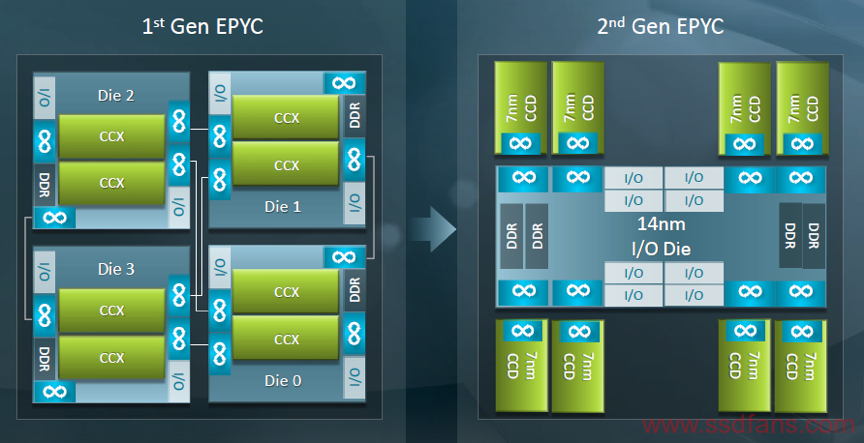

Rome的第二代EPYC已经解决了这个问题。中央处理器设计实现了一个中央输入输出集线器,所有芯片外的通信都通过该集线器进行。完整的设计使用了八个核心小芯片,称为核心复合芯片(CCDs),一个用于输入/输出的中心芯片,称为输入/输出芯片(IOD)。所有的CCD通过专用的高速无限光纤(IF)链路与这个中央I/O中心进行通信,通过这个核心可以与内部的DRAM和PCIe通道或其他核心进行通信。

CCD由两个四核核心复合体组成(1个CCD= 2个CCX)。每个CCX由四个内核和16mb L3缓存组成,位于Rome的中心。顶级64核Rome处理器总共有16个CCX,而那些CCX处理器只能通过中央输入输出芯片相互通信。没有片CCD通信。

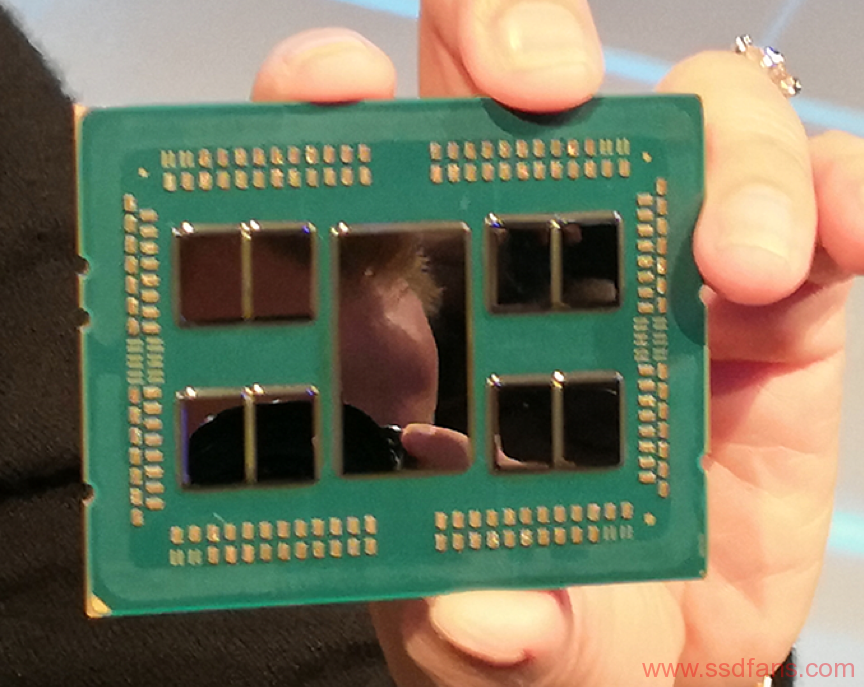

上图中,左边是第一代EPYC Naples,使用了四个Zepellin模具每个都用IF链接连接到另一个。右边是Rome,外部有8个绿色的CCD,中间是一个中央IO die,有DDR和PCIe接口。

据报道,CCD是在台积电制造的,使用的是台积电最新的7nm制程技术。相比之下,IO芯片是建立在GlobalFoundries的14nm工艺基础上的。与缓存、处理和逻辑电路相比,I/O电路很难缩小到更小的处理节点,AMD采取了一种聪明的做法,使用非常成熟的过程技术来缩短上市时间,而且肯定有很大优势。

这种拓扑结构图:

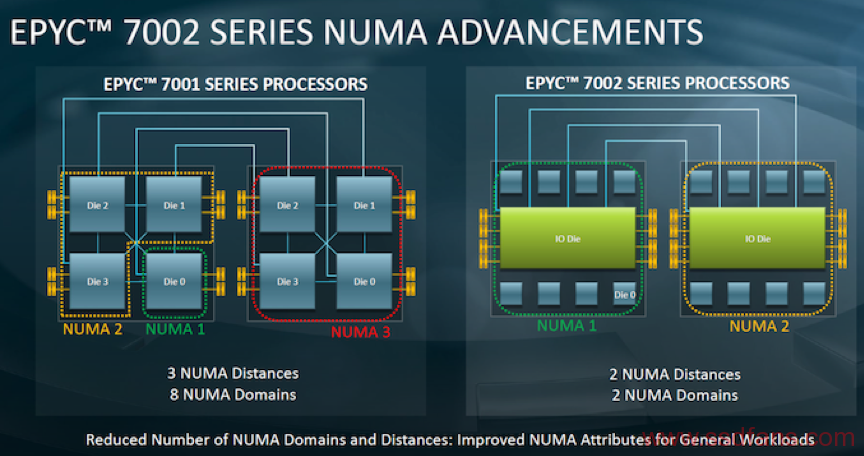

其主要优势在于,与Naples相比,第二代“EPYC 7002”系列更易于理解和优化。最终,每个处理器只有一个内存延迟环境,因为每个内核同时与所有八个内存通道通话的延迟相同。与第一代Naples相比,由于后者直接连接内存,每个CPU有两个NUMA区域。

如下图所示,这意味着在双插槽设置中,Naples处理器将像大多数软件工程师熟悉的传统NUMA环境一样工作。

最终,实现这一点的唯一方法是使用大型单片芯片,对于较小的工艺节点来说,在产量和定价方面,这种方法越来越不可取。在这方面,AMD在以高产量开发7纳米小芯片方面具有显著优势,并且在频率方面也具有显著优势。

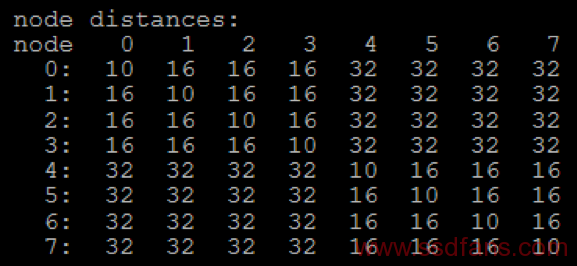

对于系统来说,NUMA环境非常有趣。对于Naples EPYC 7001中央处理器,这在双插槽设置中相当复杂:

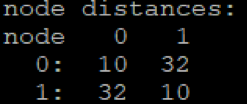

这里,每个数字都显示了访问每个其他NUMA域的延迟的“权重”。在同一个域中,权重只有10,但同一芯片上的NUMA域的权重为16。不考虑芯片时这个数值上升到了32。

这在Rome EPYC 7002上发生了显著变化:

虽然在某些情况下,EPYC 7001处理器的通信速度更快,但是从软件的角度来看,拓扑结构要简单得多,这一点很有价值。它可以保证从芯片中获得良好的性能,这将在企业中节省大量资金,同时也有助于加快商用速度。

参考链接:https://www.anandtech.com/show/14694/amd-rome-epyc-2nd-gen/2