作者 和风

SSD是目前非常流行的存储设备,相比传统的机械硬盘,因为不需要机械部件的移动就可以完成对底层介质的访问,SSD从访问时间,吞吐率等方面都有相当的优势。这就使得SSD可以很好得适应如数据库访问,缓存分层,高性能集成系统的数据共享,本地数据以及混合云存储的各种对高性能数据访问要求较高的领域。

作为SSD的底层存储介质,NAND的存储密度很高,读取与写入的速度也很可观。然而其保存内容的可靠性并不是很出色。而且随着擦写次数的增加,NAND的时间稳定性也会变得越来越差。

当NAND闪存的特征尺寸逐渐变小,在一个存储单元上存储数据位数逐渐增加,它上面所保存的用户数据也面临着逐渐增加的丢失或错误的风险。我们知道NAND的存储页面相比NOR来讲要大很多,如果仅仅因为几个或者几十个bit的反转导致的错误就要丢掉一整页是非常不经济的。ECC可以通过引入一部分冗余信息对用户数据进行校验,当部分数据发生错误时,通过冗余信息就可以有机会把错误纠正回来,从而避免因为少量错误就丢掉一整个页面。

一个NAND的页面大概会有16KB以上的存储空间,由两部分组成,其中一部分用来存储用户数据,另一部分则用来存储ECC的校验位。如下图所示。

|

用户数据 |

ECC |

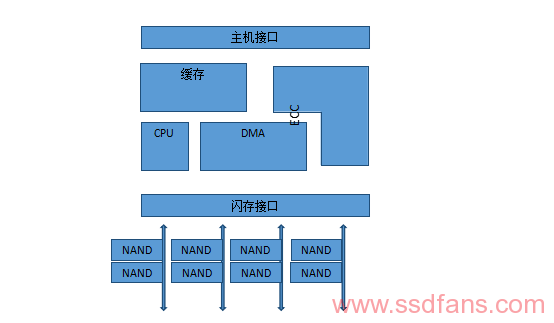

ECC引擎在一个基于NAND闪存的存储设备中所处的位置如下图所示。

BCH ECC由生成多项式所定义,当我们选定一个生成多项式以后,可以根据这个生成多项式提前计算得出编码矩阵。ECC的线性特性使得我们可以很容易地根据流过编码引擎的用户数据通过查表以及简单的移位运算计算得出ECC的校验位。编码逻辑较为简单,一般与数据的传输时钟相匹配,从而避免时钟跨域的问题。

BCH ECC的解码电路相对比较复杂,一般来说由三部分组成。第一部分负责读取带有错误比特的数据,通过对数据的校验,计算得出与错误图样相对应的伴随式;第二部分接收到由第一部分计算得出的伴随式后,通过BM算法迭代求解,可以获得一个多项式,这个多项式的解与数据中的错误图样是直接相关的;第三部分接收到错误位置多项式以后,通过Chien搜索算法来尝试获得该多项式的解,从而发现错误图样中的错误比特位置。

第一部分的逻辑较为简单,与编码逻辑类似,完成的是多项式除法的运算。可以使用与数据传输同样的时钟。

第二部分结构较为复杂,而且运算过程中需要对数据做多次缓存,逻辑量中等。

第三部分结构较为简单,然而为了提高整个解码部分的吞吐率,往往会增加搜索的并行度,这样逻辑量就会迅速增加;同时,这一部分的计算容易流水线化,比较容易提高时钟频率,这就使得在多个NAND通道之间共享提供了可能。

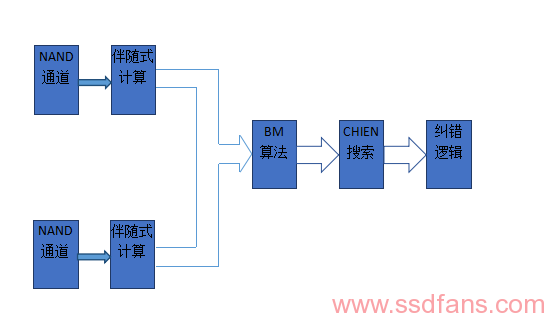

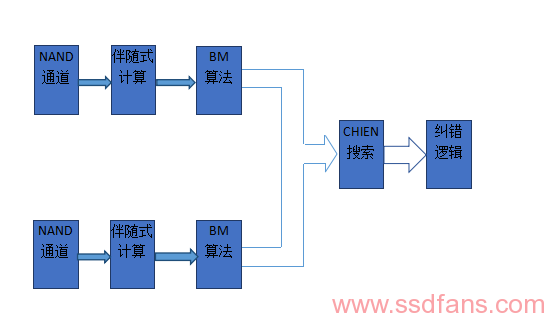

根据上面的分析,BCH ECC的解码逻辑有多种共享方式,下面为两个示例:

-

-

仅共享第三部分

因为后面两个部分的频率可以相对提高,这样可以将多个NAND通道的伴随式计算,BM算法运行时在时间上做复用处理。通过共享复杂的,容易提高频率、吞吐量的逻辑部分,可以达到简化设计、节约芯片面积的目的。