PCISIG是个大家庭,没事会弄个Compliance Workshop, 各公司可以把自己的产品拿去测试:

-

Electrical Testing – Examines platform and add-in card Transmitter and Receiver characteristics

-

Configuration Testing – Examines configuration space in PCIe devices

-

Link Protocol Testing – Examines device’s link-level protocol behavior

-

Transaction Protocol Testing – Examines devices transaction-level protocol behavior

-

Platform BIOS Testing – Examines BIOS ability to recognize and configure PCIe devices

贵司弄出一块PCIe SSD,如果能走完这一套流程,说明PCIe Interface这块没啥问题了,毕竟这些个测试项目是制定PCIe协议的组织官方出品。

然后PCISIG会给贵司一个小红花,将这块PCIe SSD放到光荣榜上 (Integrators List)

https://pcisig.com/developers/integrators-list

以上环节,贵司都是一个人在战斗,就像比武招亲,只能跟你未来老婆打,不能跟别的选手接触 (这个比武招亲是一妻多夫制)

Workshop里还有一个华山论剑的环节,各家公司可以把自家产品拿出来跟其他公司的产品放到一起切磋一下,看看互相之间组队有没有问题,这个环节就是Interoperability Test。

贵司拿着刚出炉的PCIe SSD, 走到Intel的展位:”兄台,小弟这有一块PCIe Gen3x4的NVMe SSD,想跟您的Skylake切磋一下,请赐教!” Intel的兄弟瞟了一眼你的Badge,亲切的说:”滚!” (在这个环节,确实可以礼貌的拒绝) 。

AMD在忙着跟三星,Marvell玩,也暂时没空搭理贵司。

这时,和蔼可亲的Synopsys凑了上来:”这位小兄弟,我看你骨骼清奇,未来必成大器…”

于是你们两家摆开阵势,按照下面流程开始切磋:

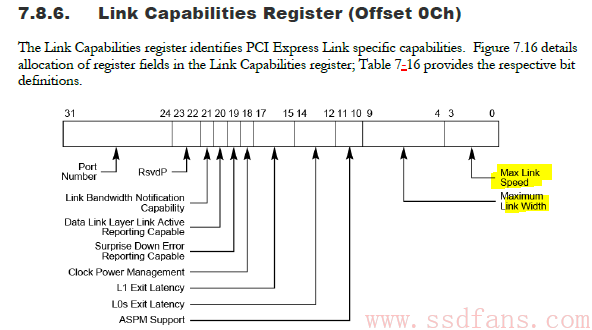

- 了解对方的实力 – “你们小区停车费多少钱一个月?” , 了解双方各自的Link Speed (Link Capability Register[3:0])和Link Width (Link Capability Register[9:4])

-

假设贵司PCIe SSD最高到 Gen3x4, Synopsys RC最高到 Gen3x16

- 把你的PCIe SSD插到Synopsys带来的开发板上 (Synopsys卖IP,不卖产品)

- 开机,检查你的PCIe SSD被OS识别到(过程中可能会提示安装驱动),检查Link Status Register确定link状态是Gen3x4

-

如果你的PCIe SSD还支持其他lane width – 比如x1,用胶布或者Reducer把lane width降到x1, 重复上述步骤,确保x1也能正常工作

- Speed和Width正确还没完,还需要做一下简单的数据,确保data能顺利通过PCIe Bus

PS:PCISIG贴心的为初入江湖的你提供了方便查看PCIe Register的工具, PCITree http://www.pcitree.de/

以上都顺利通过,把你们俩的交手记录上传到PCISIG的服务器上,继续去找其他RC或者Switch供应商。

写在最后,台上一分钟,台下十年功,为了在Workshop的Interoperability环节有好的表现,在下山前就应该找来各家的RC做相关的测试。

比如先定一个能达到小目标,Intel,ASUS, Gigabyte最新次新的主板来个10块,开机上电检查Link Speed/width,每台机器先过个200次 (此处需要Automation)。