自从Google I/O大会和阿法狗围棋显神威之后,TPU这个幕后英雄迅速受到大家的关注。本文就来一探TPU1处理器最为神秘的芯片架构。

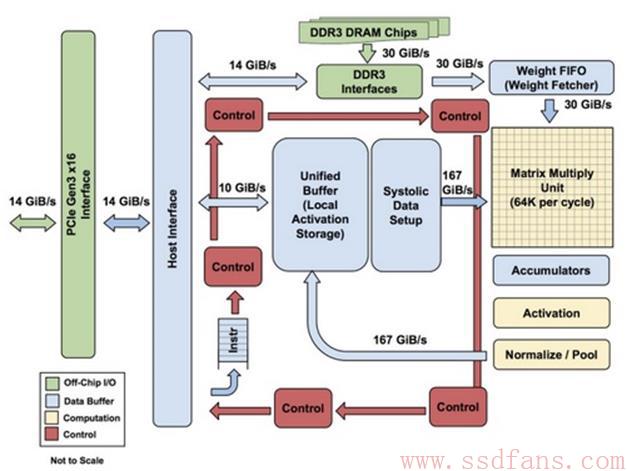

TPU的架构如下图,绿色的DDR3 DRAM是芯片外的。TPU能够像GPU和CPU一样编程,有一套CISC指令集。作为机器学习处理器,不仅仅支持某一种神经网络,而是支持很多种,比如卷积神经网络、LSTM、全连接网络等。

图中,计算逻辑是黄格子的矩阵乘法器。左下角的Instr是指令缓存。通过PCIe获得数据和指令,由控制逻辑解析指令,交给计算单元去算。有点像是DSP芯片。由于每秒支持64K次乘法,所以神经网络计算的权值数据量很大,来自于DDR3 DRAM,看上图矩阵乘法器上面的就是这路数据。但是,矩阵乘法器左边还有个Systolic来的数据,是激活量。

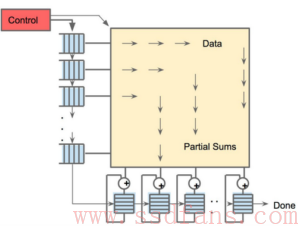

Systolic是个什么东东?翻译过来叫做心脏收缩,在体系结构里面成为脉动阵列。如下图,DM是存储器,PU是计算器,数据一波一波从DM流入PU计算,再流到DM存储,所以看起来像心脏脉动血流一样。

TPU的脉动阵列是下面的样子,作为256×256的阵列,参数送进来之后,阵列就是个二维的并行流水线乘法器,数据一波波脉动流走。

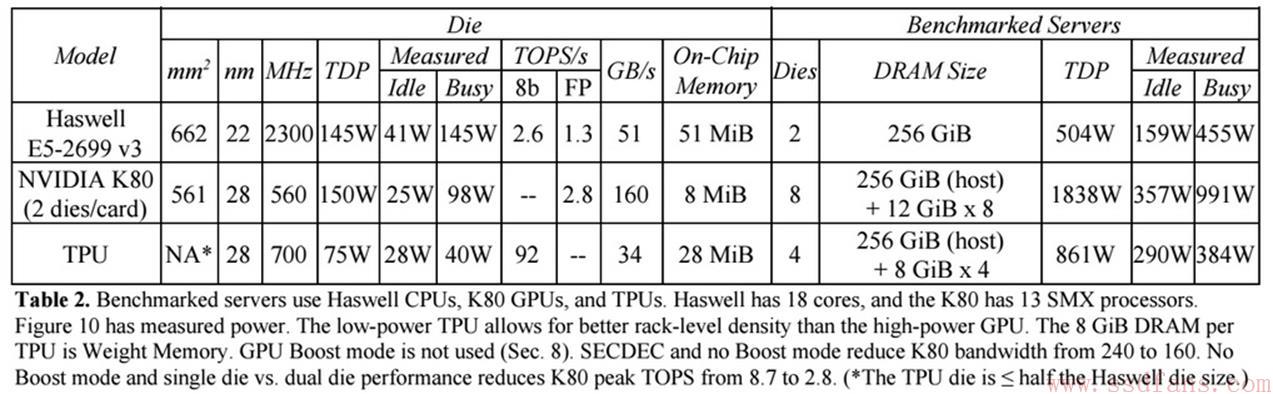

Google给出了一个GPU,Intel Xeon E5 v3 CPU和TPU的性能对比,如下。看得出来,TPU的工作功耗最低,GPU最高。从TOPS看,TPU性能是CPU的35倍,推算是K80 GPU的17倍。

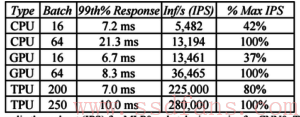

再来看看真实的深度学习预测计算的性能。Batch越大,意味着计算量越大,TPU承受了最大的Batch,却实现了最高的IPS,就是每秒算多少次。是GPU的近10倍。

其实Google最早是计划用FPGA的,但是财大气粗,考虑到自己的特殊应用,就招了很多牛人来做专用芯片TPU。对于大部分有志于此,但是经费没人家多的公司来说,FPGA是个更好的方案。