前面有篇文章介绍过Seagate的LDPC,其中提到了动态ECC的部分,说的是在SSD不同的生命阶段,采用不同的ECC长度。

这两天看到了一份MicroSemi的资料,也提到了动态ECC的部分,可以分享一下。

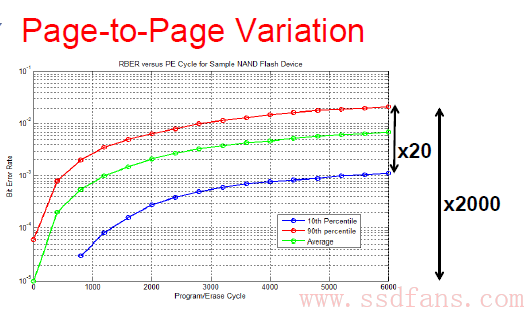

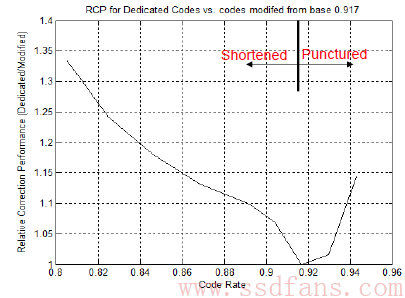

首先,MicroSemi给出一张图说明自己的观点:

- 相同的PE Cycle,不同的Page之间,RBER最多可能相差20倍

- 不同的Page,在整个生命周期内,RBER最多可能相差2000倍

这样会带来一个问题:

- 如果Parity Data占用比较多bit,User Data可用空间就小,WA就大

- 如果Parity Data占用比较少bit,有些page就会出现Uncorrectable Error

所以,主控要能够提供多种ECC长度供固件选择为好,MicroSemi给了三种:

- Puncturing (裁剪)

- Shortening (瘦身)

- Custom Code Rates (定制)

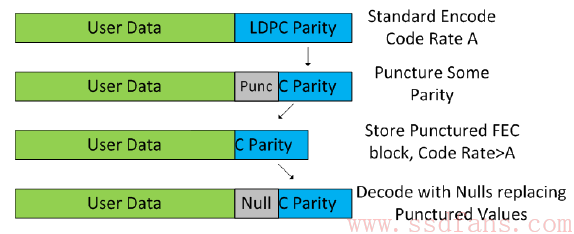

Puncturing是对Parity Data动刀:

写: 原本User Data需要10 bit Parity,砍掉2bit,再写入NAND

读:从NAND读出数据,将8 bit Parity补上2 bit (null)再Decode

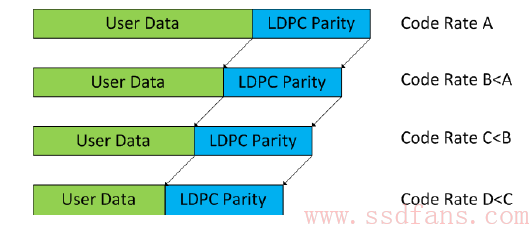

Shortening是对User Data动刀:

Parity长度不变,但是User Data长度变化,变相调节了单位User data对应Parity的位数;

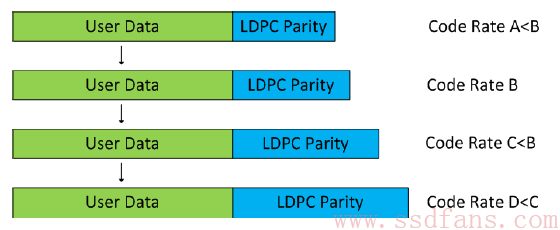

Custom code rate就是量身定做了,固定的User Data长度,Parity你想用多少位就用多少位;

从MicroSemi放出的结果来看:

采用定制的Code能够比前两种方式最多提高30%的解码性能以及减少20%的解码迭代次数。

我有两个疑问:

- 主控提供了这样的机制,固件应该根据什么信息决定每一笔数据写入时的ECC长度?是不是在FTL映射出PBA时,还需要读出该地址上次读取数据时的RBER?

- 大家都搞动态ECC,这东西能申请专利不?如果可以,是不是A就可以告B然后坐等收钱了?c

原文:LDPC Code Rate Adaptation Methods for NAND Flash on FMS 2016