作者:望月闲人

上电,复位和初始化,还有独特的第四个步骤!

想要和望月闲人还有全世界的大牛讨论SSD及存储相关技术?加nanoarch为微信好友,拉你进ssdfans微信群 。

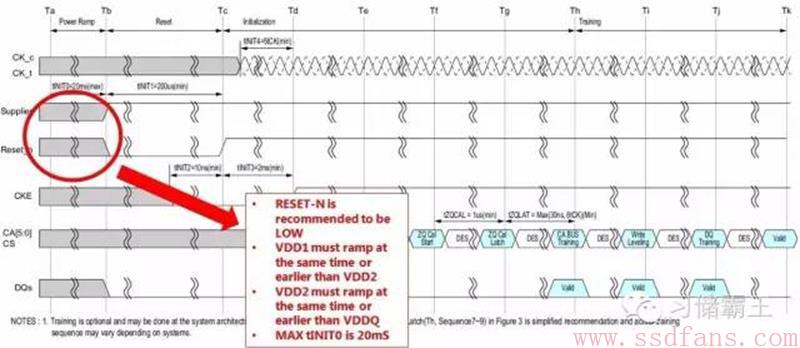

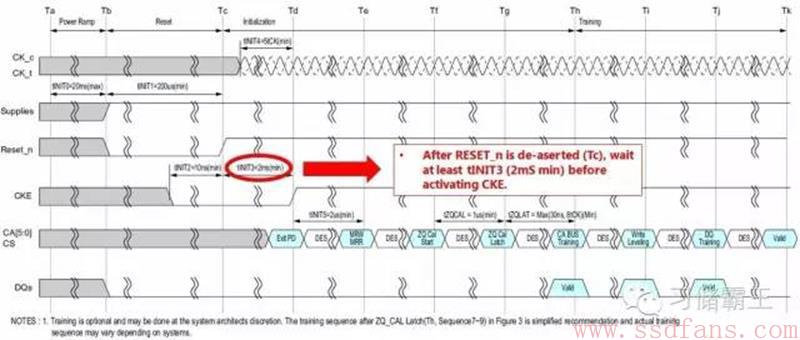

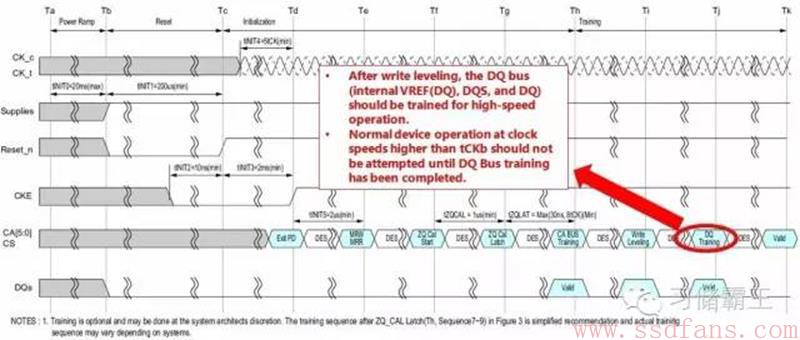

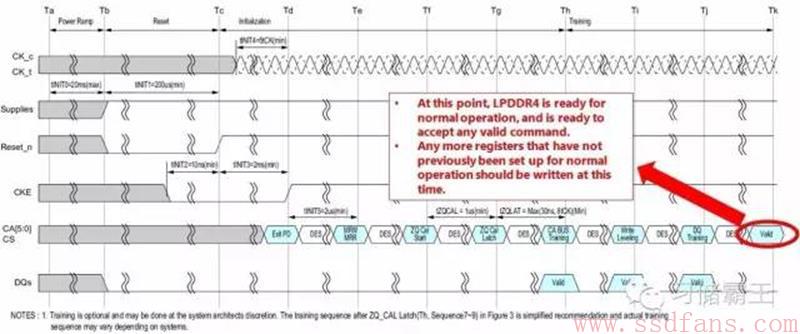

先看看下面这个图对整个初始化过程有个总体的了解,LPDDR4初始化主要分下面四个阶段:Power Ramp, Reset, Initialization和training。上电,复位和初始化大家一定都比较熟悉,任何设备都要经过这三个步骤才能boot起来,只是每个设备的要求不同,倒是第四个阶段training看起来有点新鲜感。不急,step by step。

1. After Ta

Ta时刻的开始是以VDD1上电为标志,进入到Power Ramp阶段,这段时间要求Reset信号拉低,VDD2上电不早于VDD1上电,VDDQ上电不早于VDD2上电。以VDD1上电开始到VDDQ上电结束,这段时间tINIT0要求最大不能超过20mS。

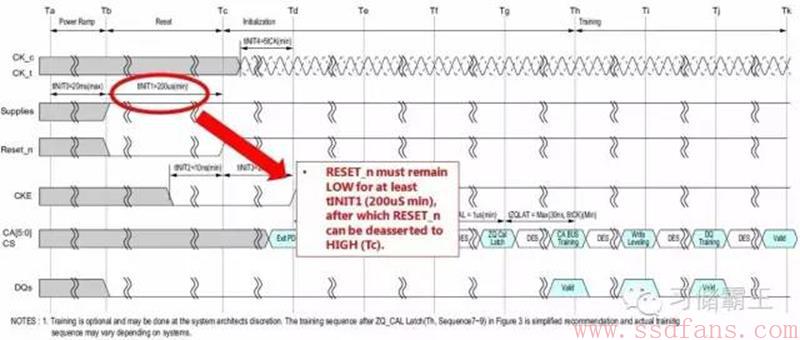

2. After Tb

以VDDQ上电完成为标志,进入到reset阶段。这里reset信号要保证至少保持tINIT1=200uS(min)低电平之后才可以拉高。

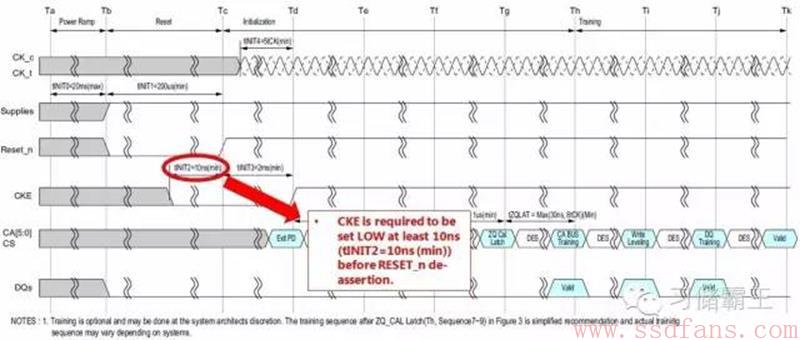

在RESET_N拉高之前,CKE必须要设置成低电平至少10nS(tINIT2=10ns(min))

3. After Tc

Reset_n信号线拉高时刻为Tc,进入到下一个阶段initialization。tINIT3(reset信号线拉高到CKE拉高)至少要保持2mS。

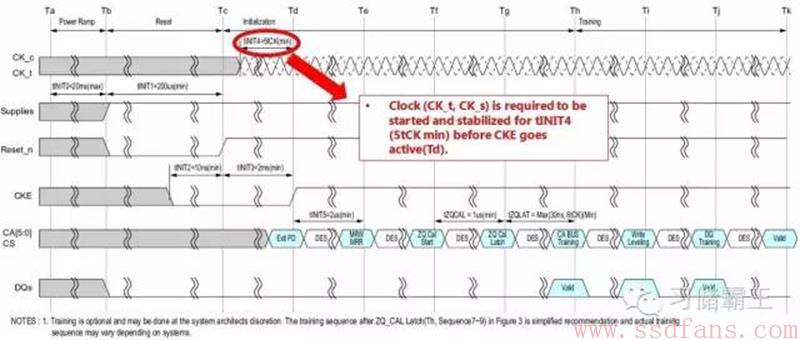

在CKE使能拉高之前,CK_t和CK_s时钟差分信号要求开始并保持至少tINIT4(最少5个时钟周期)。

4. After Td

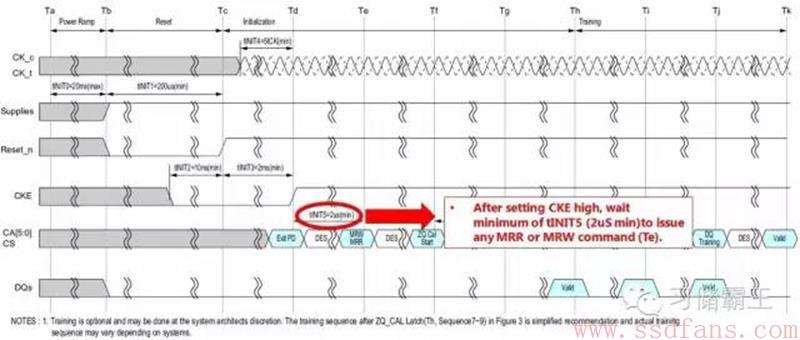

CKE拉高时刻为Td, Td后必须要等待至少tINIT5=2uS才可以发MRR或者MRW命令对mode register寄存器开始操作。

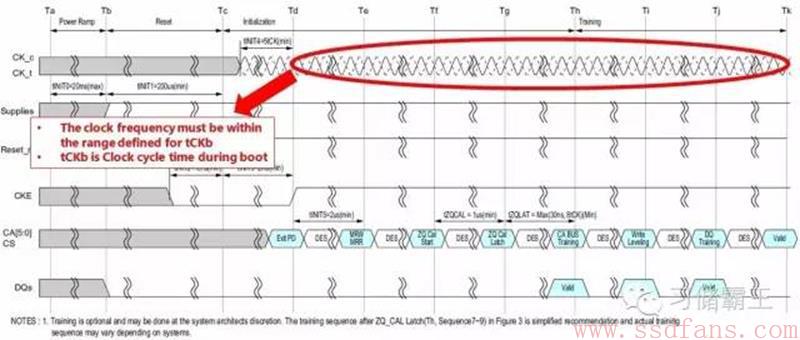

在整个初始化过程中,时钟频率必须要在tCKb规定的范围内,tCKb到底是多少要根据芯片手册的定义。

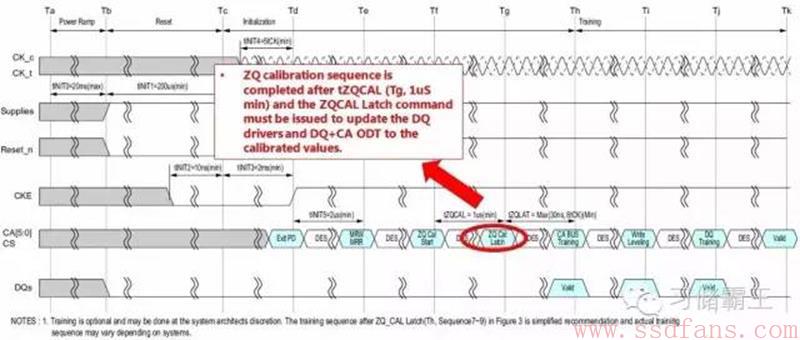

5. After Te

在通过MRW完成上拉下拉电阻值和RX termination值的设置之后,SoC的DRAM控制器就可以发ZQ校准命令“ZQCAL Start”了。(ZQCAL命令是用于校准在不同电压和温度下VOH level和输出电阻的)

6. After Tf

在发出ZQ校准命令之后等待tZQCAL(最小1uS),然后发送ZQCAL Latch命令更新校准参数(DQ驱动能力,DQ/CA ODT的校准值)。

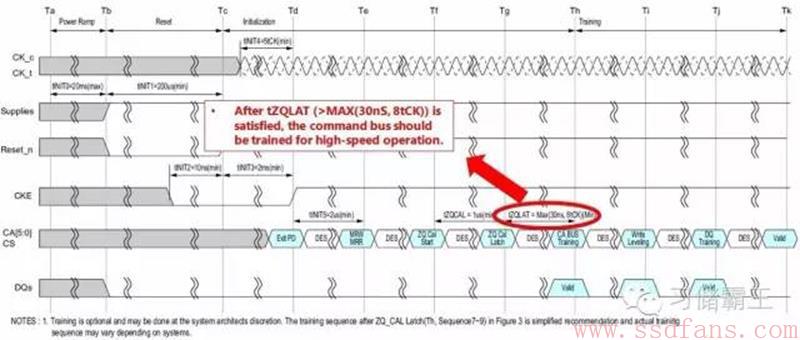

7. After Tg

满足tZQLAT(>MAX(30nS, 8tCK))被满足之后,

命令总线开始做training为高速操作做准备。

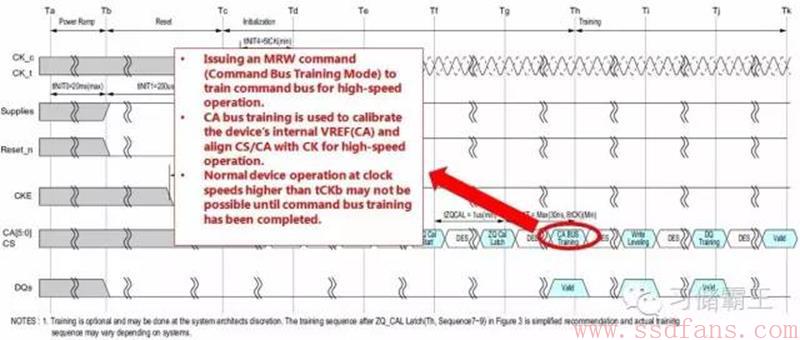

发送MRW命令使LP4进入到command bus training mode开始对command bus做training。CA bus training主要是用来校准device内部CA的参考电压VREF(CA) 和高速工作条件下CS/CA和CK之间的时序。

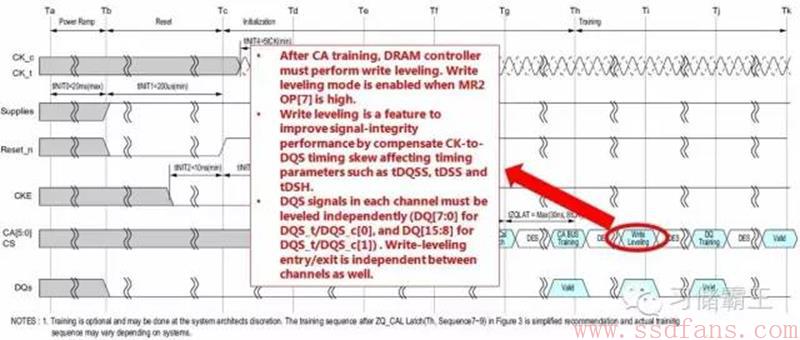

8. After Th

CA bus training结束之后,DRAM要设MR2 OP[7]高来执行write leveling操作。Writing leveling是通过补偿CK-DQS之间的时序关系(tDQSS, tDSS和tDSH)来改善信号完整性的feature。DQS信号做write leveling必须是每个channel独立做的,进入和退出也是channel独立的。(DQ[7:0] for DQS_t/DQS_c[0], DQ[15:8] for DQS_t/DQS_c[1])

9. After Ti

Writing leveling之后,开始DQ总线的training(internal VREF(DQ), DQS和DQ)。在DQ总线training完成前,采用高于tCKb的时钟操作是不允许的。

10. After Tj

DQ training结束后就可以开始正常的操作并可以准备接收命令了,并且之前没有写的MR寄存器在这里要被设置好。

至此,整个LPDDR4的初始化到此完成。

不想错过望月闲人的后续精彩文章?长按或扫描下面二维码关注ssdfans就可以了!

公司招聘:

深圳大普微电子招聘,SSD芯片设计,固件开发,机器学习相关人才!

上海飞斯招聘: 存储开发工程师,RAID、USB、SATA、AHCI、NVME、FTL、文件系统的开发及调试

记忆科技上海UFS FW内推机会,UFS FW开发