作者 琥珀

因为CNN的特有计算模式,通用处理器对于CNN实现效率并不高,不能满足性能要求。 因此,近来已经提出了基于FPGA,GPU甚至ASIC设计的各种加速器来提高CNN设计的性能。 在这些方法中,基于FPGA的加速器引起了研究人员越来越多的关注,因为它们具有性能好,能源效率高,开发周期快,重构能力强等优点。

在实验中,研究人员发现在FPGA相同的逻辑资源利用率情况下,两种不同解决方案可能会有多达90%的性能差异。所以找出最佳解决方案是很重要的,特别是当考虑到FPGA平台的计算资源和存储器带宽的限制时。 实际上,如果加速器结构没有精心设计,其计算吞吐量与提供FPGA平台的内存带宽不匹配。 这意味着由于逻辑资源或存储器带宽的利用不足将造成性能的降级。

不幸的是,FPGA技术和深度学习算法的进步同时加剧了这个问题。 一方面,由最先进的FPGA平台提供的日益增加的逻辑资源和存储器带宽扩大了设计空间。 此外,当应用各种FPGA优化技术(如循环平铺和变换)时,设计空间进一步扩大。 另一方面,为了适应现代应用的需求,深度学习算法的规模和复杂性也在不断增加。所以,在设计空间中找出最优解是比较困难的。 因此,迫切需要有效的方法来探索基于FPGA的CNN设计空间。

然而现有的大部分工作主要关注计算引擎优化,它们有的忽略外部存储器操作,有的将其加速器直接连接到外部存储器。还有些研究工作通过精细的数据重用减少外部数据访问来加速CNN应用。然而,这种方法并不一定会导致最佳的整体性能。此外,这种方法需要重新配置不同层次的FPGA计算。这在某些情况下是不可行的。

因此,为了有效地探索设计空间,有研究人员提出了一种分析设计方案。这种方案考虑到缓冲区管理和带宽优化,以更好地利用FPGA资源并实现更高的性能。同时加速器能够跨越不同的层执行加速作业,而无需重新编程FPGA。下面我们具体来看一下这种方案。

考虑到在应用中基本都是将训练好的CNN模型部署到现有计算平台上进行预测操作,所以,很多的FPGA加速方案中仅考虑优化前向操作。同时又有研究表明,卷积操作占据了CNN模型将近90%的计算时间,所以,本方案也是仅考虑优化CNN模型前向计算中的卷积运算,优化的模型选择为经典的AlexNet。同时为了更好的分析网络的性能,研究人员借助Roofline Model进行优化方案的设计。通过这个 model,既可以评估一个设计的效率,还能很容易看出设计到底是 computation-limited 还是 memory bandwidth-limited,可以帮助确定进一步优化的思路。

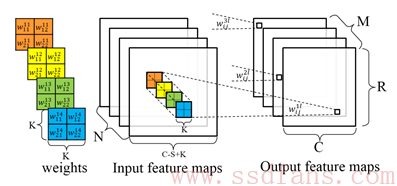

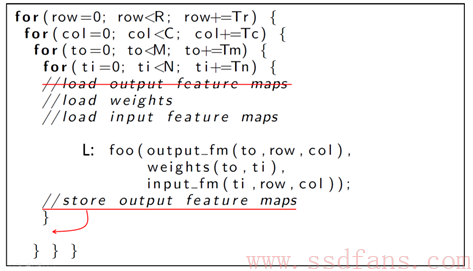

首先,我们先来了解一下CNN中的卷积运算的规则,CNN中的卷积运算如图1所示,代码1表示其伪代码。

图1

代码1

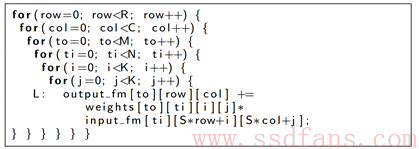

几乎所有的基于FPGA的加速方案,都如图2显示的那样,FPGA上的CNN加速器设计主要由处理元件(PE),片上缓冲器,外部存储器和片上/片外互连几个组件组成。其中PE是卷积的基本计算单元。用于处理的所有数据都存储在外部存储器中。由于片上资源限制,数据首先被缓存在片上缓冲区中,然后再馈送给PE。双缓冲区用于通过数据传输时间来覆盖计算时间。片内互连专用于PE和片上缓冲存储器之间的数据通信。

图2

通过观察图2,我们可以发现有几个设计问题妨碍了FPGA平台上高效的CNN加速器设计。首先,为了适应芯片上的一小部分数据,循环平铺是必须的。不正确的平铺可能会降低数据重用的效率和数据处理的并行性。第二,应仔细考虑PE和缓冲库的组织以及它们之间的互连,以便有效地处理片上数据。第三,PE的数据处理吞吐量应与FPGA平台提供的片外带宽匹配。

为了解决上述问题,下面逐条分解实现方案。

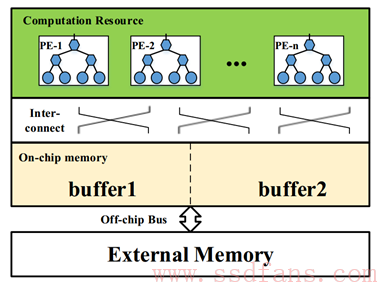

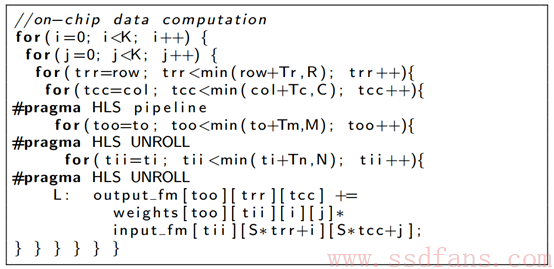

1)首先,方案采用循环平铺(代码2)。注意,循环迭代器i和j由于CNN中卷积窗口大小K的相对小的尺寸(通常在3到11之间)而不是平铺的。其他循环迭代器(row,col,to和ti)平铺到图形循环和点循环中(代码2中的trr,tcc和tii)。

代码2

2)片上计算优化的实现

计算优化的目的是在充分利用FPGA硬件平台提供的所有计算资源的同时,实现高效的循环展开/流水线化。

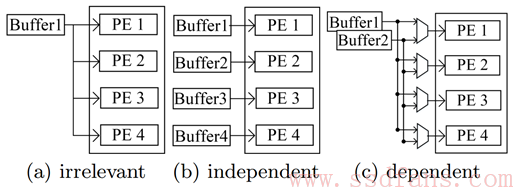

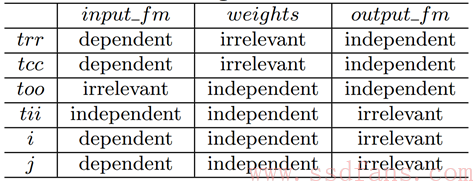

循环展开可用于增加FPGA设备中大规模计算资源的利用率。在给定阵列上循环维度的不同循环迭代之间的数据共享关系可分为三类:不相干,独立,有依赖关系。对应如图3所示。如代码2所示,CNN代码中的数据共享关系如表1所示。

图3

表1

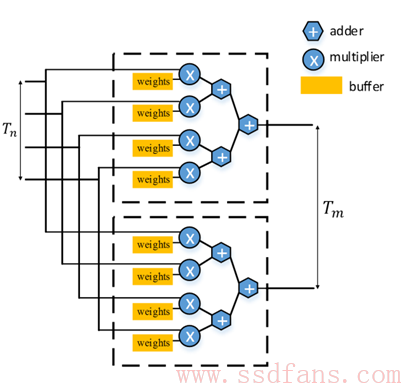

因此在设计展开时,选择对too和tii进行展开,以避免所有阵列的复杂连接拓扑。too和tii被置换到最内层循环,以简化HLS代码生成。生成的硬件实现如图4所示。

图4

循环流水线化是高级合成中的关键优化技术,通过重复来自不同循环迭代的操作的执行来提高系统吞吐量。因此方案使用基于多面体的优化框架来执行自动循环变换以将并行循环水平置换到最内层,以避免循环依赖。

最终循环展开和循环流水线优化后的代码结构如代码3所示。

代码3

3)内存访问优化的实现

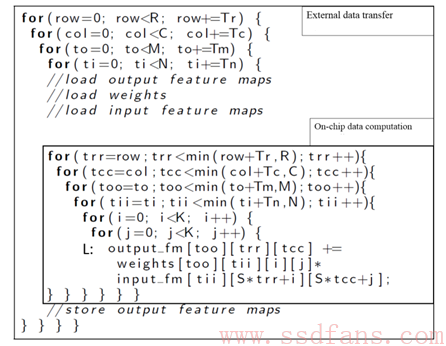

代码4展示了一个CNN层的存储器传送操作。输入/输出特征图和权重在计算引擎启动之前就已被加载,计算完成后,将生成的输出特征图写回主存储器。

代码4

通过分析可知,通信部分中的最内层循环(代码4中的ti)与数组无关,因此在不同的循环迭代之间存在冗余的存储器操作。所以方案使用本地存储提升来减少相关冗余操作。代码4中,最内圈的维数ti与阵列输出特征图无关。因此,可以将对阵列输出特征图的访问提升到外部循环。请注意,升级过程可以迭代执行,直到访问周围的最内层循环最终相关。通过本地存储提升,阵列输出特征图上的存储访问操作的行程计数从降到了 。

循环转换数据重用。为了通过本地存储提升最大化数据重用的机会,方案使用基于多面体的优化框架来识别所有合法的循环转换。表2显示了循环迭代和数组之间的数据共享关系。每个合法循环调度中都会使用本地存储提升功能,以减少总通信量。

表2

通过上述操作,方案明显提升了CTC Ratio。

4)设计空间探索

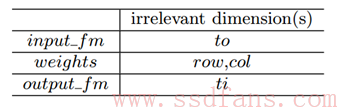

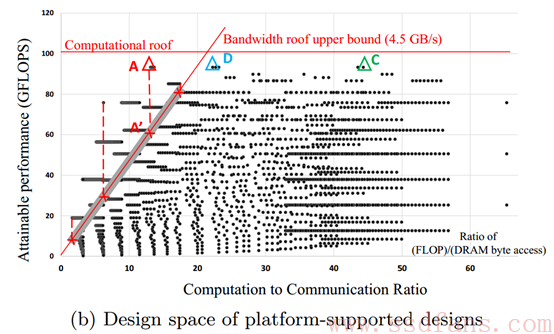

以CNN模型的第5层为例,图5描绘了CNN模型的第5层在rooline模型坐标系中的所有合理的解决方案。横轴表示CCT Ratio,纵轴表示计算性能(GFLOPS)。任何点与原点(0,0)之间的线的斜率表示该实现的最小带宽要求。

图5

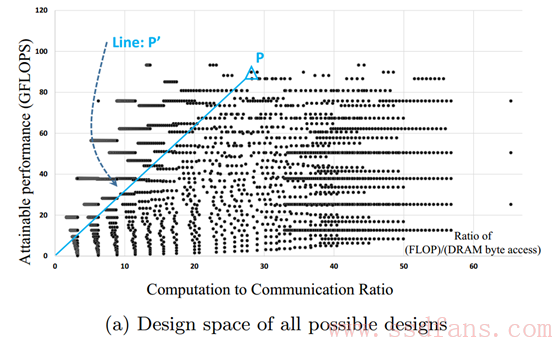

图6中,带宽Roof和计算Roof的线由平台的规格定义。带宽Roof线的左侧的任何一点都需要比平台提供的带宽更高的带宽。例如,尽管图中A方案实现了最高的计算性能,但是目标平台无法满足该方案所需的存储器带宽。所以,综合分析比较,最终选择方案C作为第5层的设计方案,它的带宽要求为2.2GB/s。

图6

5)多层CNN加速器设计

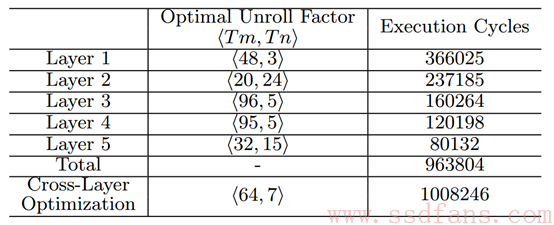

在此之前,我们讨论了如何找到每个卷积层的最优实现方案。但是,在CNN应用中,这些参数可能在不同的层之间需要变化。表3描述了该应用CNN模型中所有层的最优展开因子(Tm和Tn)。为了解决这个问题,本方案采用的方法是在不同卷积层之间设计具有均匀展开因子的硬件架构。具有统一展开因子的CNN加速器设计和实现简单,但可能对某些层是次优的。表3显示,使用统一展开因子<64,7>,与每个优化卷积层的总执行周期相比,退化在5%以内。因此,方案选择了CNN加速器在卷积层上的统一展开因子。

表3

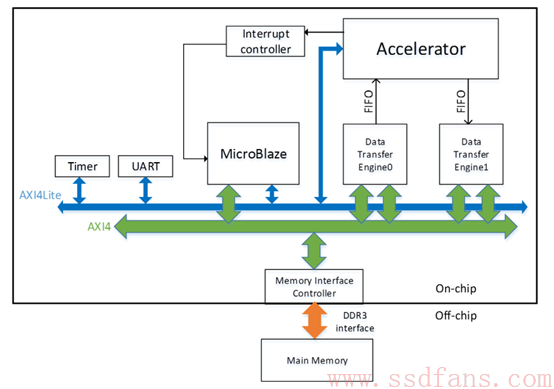

解决完上述问题,图7就是整个实现方案架构。实验是在具有Xilinx FPGA芯片Virtex7 485t的VC707板上完成。其工作频率为100 MHz。 为了比较性能,CPU软件实现在具有15MB高速缓存的Intel Xeon CPU E5-2430(@ 2.20GHz)上运行。

图7

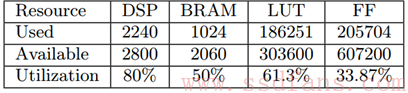

该实验的资源利用情况如表4所示。

表4

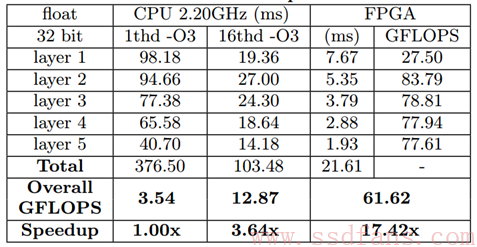

加速器的性能比较如表5所示。

表5

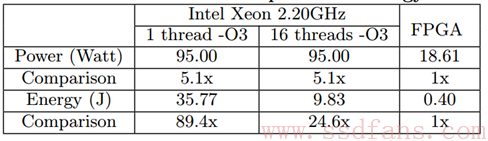

表6显示,CPU软件实现和FPGA实现之间的消耗能量的比例至少为24.6x。 FPGA实现使用的能量远远低于其CPU实现。

表6

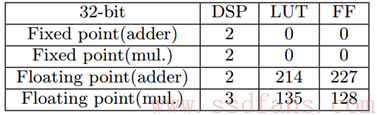

同时,如表7所示,如果使用定点计算引擎,该设计方案可以实现更好的性能和性能密度,因为定点处理元件使用的资源少得多。

表7

参考文献:

[1] Zhang C, Li P, Sun G, et al. Optimizing fpga-based accelerator design for deep convolutional neural networks[C] Proceedings of the 2015 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays. ACM, 2015: 161-170.