异步时序

闪存接口有同步异步之分,一般来说,异步传输速率慢,同步传输速率快。异步接口没有时钟,每个数据读由一次RE_n信号触发,每个数据写由一次WE_n信号触发。同步接口有一个时钟信号,数据读写和时钟同步。

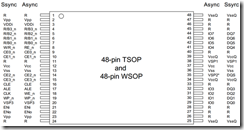

我们先来看看ONFI2.3协议规定的一个典型的闪存芯片管脚图。这个芯片对外输出数据位宽为8 bit,Ssync是同步,Async是异步。

图1-1 闪存芯片管脚图

比较一下两种接口下的管脚定义,大部分都是一样的,区别就是表3-3中的四类信号。后面我们看看同步和异步的时序就能了解为什么这些信号不一样了。

表1-1 同步异步管脚定义对比

|

同步 |

异步 |

|

W/R_n |

RE_n |

|

CLK |

WE_n |

|

IO7-0 |

DQ7-0 |

|

VSP2 |

DQS |

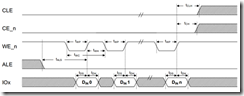

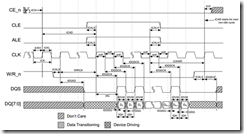

先来看看异步数据写入的时序图。

图1-2 异步写数据时序图

这张图里有5个信号:

l CLE:Command Latch Enable,CLE有效时IOx发送命令;

l CE_n:Chip Enable,这个信号来选通一个逻辑上的芯片——Target。为什么说是逻辑上的芯片?因为物理芯片里面封装了很多Target,每个Target是完全独立的,只是有可能共享数据信号,所以通过CE_n来选择当前数据传输的是哪个Target,业内一般把Target叫做CE;

l WE_n:Write Enable,写使能,这个信号是用户发给闪存的,有效时意味着用户发过来的写数据可以采样了;

l ALE:Address Latch Enable,ALE有效时IOx发送地址;

l IOx:数据总线。

同时有很多时间参数,这里只介绍几个关键的参数:

l tWP是WE_n低电平脉冲的宽度,tWH是WE_n高电平保持时间,合起来一个周期的时间就是tWC;

l tDS是数据建立时间,意思就是8比特数据要都达到稳定状态,最多这么长时间;

l tDH是数据稳定时间,这段时间里数据信号稳定,可以来采样;

这样我们来看上面的时序图,数据写入的时候,数据总线不能传输地址和命令,所以ALE和CLE无效。这个Target有数据传输,所以CE_n有效。每一个WE_n周期对应一次有效的数据传输。

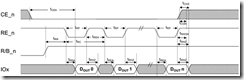

再来看看的异步数据读出时序图,多了两个信号:

l RE_n:读使能。这个信号是用户发给闪存的,每发一个读使能,闪存就在数据总线上准备好数据,等用户采样;

l R/B_n:Ready/Busy。闪存正在进行内部读的时候,Busy_n有效,当操作完成数据准备好之后,Ready有效,用户可以来读了。

所以,图就是用户向闪存发了读命令之后,Ready信号拉高,意味着数据准备好了。接着,用户发RE_n信号去读数据,每个RE_n周期,闪存发送一个有效数据到数据总线上,供用户采样。

图1-3 异步读数据时序图

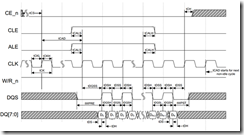

同步时序

同步时序最重要的两个信号是时钟CLK和DQS。现在的闪存基本都采用了DDR(Double Data Rate)技术,就是说每个时钟周期传输两拨数据。图3-35是同步模式下的数据写入时序图,介绍一下几个信号。

l CLK:时钟。时钟信号由用户产生,在时钟信号的上升沿和下降沿都有数据被触发,实现DDR,意味着100MHz的时钟频率数据传输速率是200MT/s。

l W/R_n:Write/Read_n。写的时候高电平,读的时候低电平。

l DQS:Data Strobe。DQS用来区分出每个数据传输周期,便于接收方准确接收数据。读数据时,DQS由闪存产生,DQS上下沿和数据对齐。写数据时,DQS由用户产生,DQS中间对应数据的中间稳定区域。所以,DQS可以看成数据的同步信号。

l DQ[7:0]:数据总线。

我们再来看看几个关键的时间参数。

l tCALS:CLE,W/R_n和ALE的建立时间。

l tDQSS:数据输入到第一个DQS跳变沿的时间。

图1-4 同步写数据时序图

了解了各种信号和时间参数,我们就能看懂上面的数据写入时序图。CLE和ALE同时有效之后的第一个CLK上升沿,数据开始准备并输出。经过tDQSS时间后,DQS开始跳变,并且跳变沿位于DQ数据信号的稳定位置。之后每半个时钟周期,输出一组数据。

再来看看下面的读数据时序图(图3-36),和写入差不多,只不过W/R_n信号是低电平,同时DQS跳变沿和数据上升沿同步。

图1-5 同步读数据时序图

闪存命令集

固态硬盘主控是通过一系列闪存命令与闪存通讯的。每款闪存芯片,都定义了其支持的命令,以ONFI 2.3协议为例,它定义的命令如表3-4。用户要使用这些功能时发送命令即可,比如读数据,就发送00h-30h,不过具体命令时序和使用方式要看专门的定义。

下面介绍一下几个比较常用的命令:

查看更多内容,扫描下图二维码,阅读原著和以上大图。