作者 唐杰

和大家一样,当NVMeoF的标准出来之后,我们也在考虑如何快速帮助客户推出性价比靠谱的产品。和大部分潜在用户讨论之后,发现使用标准的RDMA网卡这条路可能有问题,因为25G的大户,Mellanox的网卡已经号称支持NVMeoF的协议卸载(其实,我到现在都没明白,Mellanox如何做到在NVMeoF协议没有推出之前都能在ASIC上做协议卸载)。

摆在眼前的选择不多,也很明显,必须要在FPGA做Intel做了几十年的事情——集成。FPGA的好处就在这里体现了,我们可以方便地实现各种I/O的接口,并在内部通过AXI BUS进行低成本的互联。

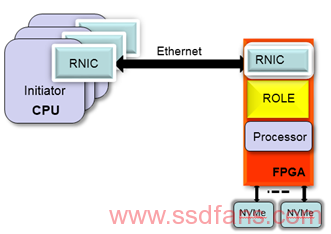

使用集成大法,使用FPGA的100G的MAC做了一个支持RoCEv2的100G RDMA Ethernet interface,使用FPGA上的硬核(ARM A-53),或者软核(MicroBlaze)做控制链路。

在NVMe后端,使用PCIE硬核+软核的方式可以支持多达8个的NVMe SSD。

从系统框图上,可以看到整个方案就是一个单芯片解决方案。可以说是把一个X86的存储机头在FPGA里进行了实现。

当然,和任何创新一样,都不是一帆风顺的。使用FPGA做RDMA的网卡并不多见,ARM的生态,特别是对于数据中心至关重要的PCIE的生态也不健全,毕竟ARM上支持一个PCIE RC 以及多个PCIE root port 都是新课题。

在FPGA中实现NVMeoF的优势也是比较明显的:

-

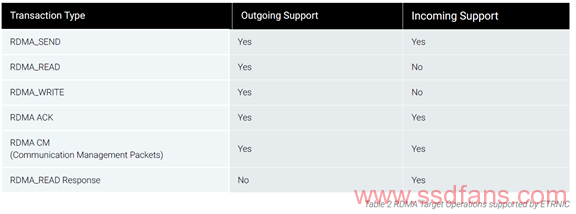

NVMeoF对于RDMA的verbs的要求很低,只用实现部分的命令,同时NVMeoF所有的I/O都是从Target发起,因此只用实现部分功能即可。

-

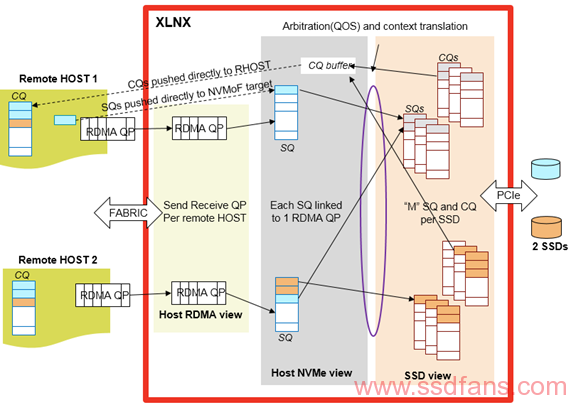

FPGA中有大量的Block RAM, 在通讯业中使用Block RAM构建多级的FIFO来实现数据管道,这NVMeoF中,可以构建面向NVMe的CQs/SQs,RDMA 网卡的QPs。利用FPGA的片上内存,可以实现clock级别的数据传输。使用了cut through的dataflow,不用使用大量的DDR来做数据缓存。

-

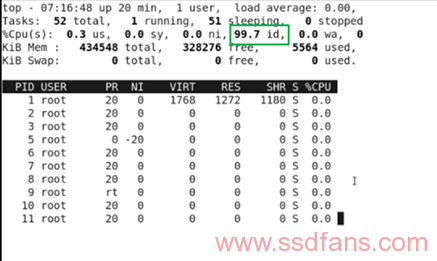

因为AI兴起了异构计算这个概念,FPGA厂商也从善如流,推出了包含ARM硬核的ZYNQ系列产品,在这里ARM可以做控制链路, 不参与数据的传输。使用ARM,也方便了我们的软件开发,目前ARM上的软件都是从Linux的upstream上移植过来,除了支持Xilinx的Petalinux以外,也会支持类似RHEL的Data Center 操作系统。在性能测试过程中, Xilinx的A-53的ARM core很淡定。

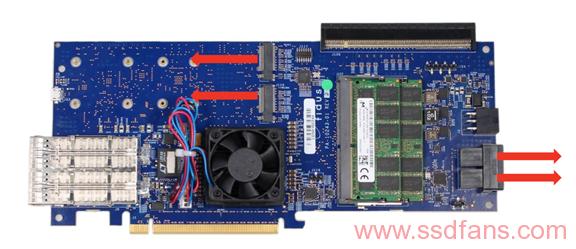

经历了种种考虑之后,Xilinx开始行动了,于是有了这个板子【1】,作为Xilinx在数据中心的I/O加速板, 实现了ARM在控制链路,数据链路在FPGA的实现。

插播广告,这个平台同样可以做对象存储的接口,实现KV store,请移步【2】。

【1】http://sidewinder.fidus.com/

【2】https://www.missinglinkelectronics.com/index.php/menu-products/key-value-store-accelerator