2019年将是PCIe的重要一年。 随着PCIe 5.0基础层0.9版的批准,实施者有了继续推进工作的坚实基础。 PCIe 4.0是在2017年推出的, PCIe 3.0版是在此前很久(2010年)在该行业中推出的。 事实上,5.0版紧随4.0版之后,许多产品可能超越4.0版本并直接进入5.0版。 每个版本的PCIe都将吞吐量提高了一倍,其中5.0版实现了63 GB / s的速度,并实现了16通道。 将其与的2003年推出的 PCIe 1.0有16个通道但吞吐量为4 GB / s。

回到1992年英特尔最初的PCI规格更令人惊讶。当时的时钟频率为33.33 MHz,32位总线的数据速率为133MB / s。 当然,最初的PCI使用并行同步数据线,由于时钟和总线仲裁问题限制了吞吐量。 所有PCIe规范都依赖于高速串行数据传输,每个连接的设备都具有专用的全双工发送和接收线对。 与现代串行链路一样,时钟嵌入在数据流中,无需外部时钟线。 多个通道用于增加吞吐量,增加了有限通道偏斜的要求,以便控制器可以重新组装条带数据。

实际上,PCIe IP的设计人员和集成PCIe 5.0的团队需要注意许多技术因素。 Synopsys最近在他们的网站上发布了一篇讨论PCIe 5.0的技术性的文章。 在32GT / s的速率下,奈奎斯特频率增加到16GHz。 用于传输数据的这种较高频率使信道设计复杂化。 在这个更高的工作频率下插入损耗增加,并且串扰成为更严重的问题。 除非可以使用重定时器,否则FR4作为PCB材料的选择完全被排除在大多数设计之外。 PCIe的最大允许通道损耗为36dB。 FR4上的16英寸100欧姆差分对带状线在16 GHz时将损失33.44。 对通道的其他元件(例如包装,连接器,电缆等)几乎没有任何损失。幸运的是,如果做出正确的设计决策,还有更好的选择。

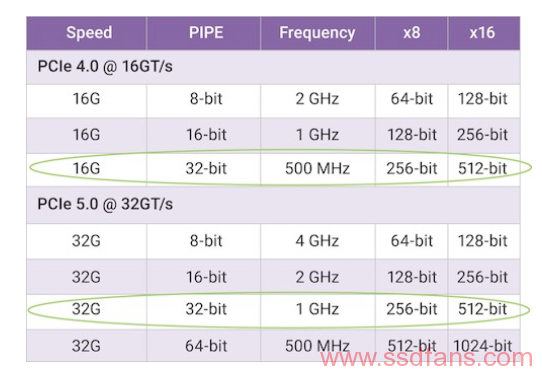

在Synopsys发布的文章中,指出PHY和控制器之间的相互作用变得更有趣。 有一个接口,称为PCIe的PHY接口(PIPE),用于集成PHY和控制器,以及支持PCIe 5.0更改的最新版本PIPE 5.1.1。 在最新版本中,通过将边带引脚移入寄存器位来减少引脚数,物理编码子层(PCS)从PHY移至控制器以允许使用更通用的PHY设计,添加了64位选项以帮助降低PIPE接口所需的速度。

Synopsys白皮书描述了以最高事务处理速率运行的8和16通道接口上的时序收敛。 使用具有32位PIPE的512位控制器,以16 GT / s(16通道)运行,控制器逻辑时序可以以1 Ghz时钟速率关闭。 其他选择要么需要更高的时钟频率,使时序收敛不可行,要么需要更大的控制器,这在当今市场上是不可用的。

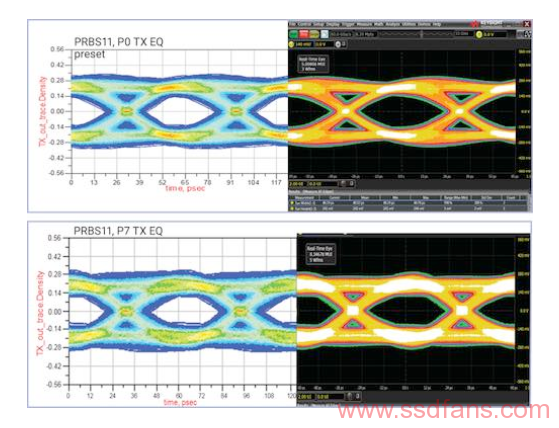

Synopsys还提供了许多有关PCIe 5.0的封装和信号完整性注意事项的有用信息。 他们总结了关于接口建模和测试的部分。

Synopsys为PCIe 5.0提供完整的解决方案,包括控制器,PHY和验证IP。 对于希望将最新一代产品添加到其产品中的设计团队来说,这应该是一种帮助。

为了给给定的应用程序构建正确的接口,需要做很多考虑和选择。 用于PCIe的Synopsys DesignWare IP包括可配置性,支持多种数据路径宽度,包括经过硅验证的512位架构。网站上关于这些的文章非常多,有助于澄清关于PCIe 5.0迁移的一些重大问题。

原文链接:https://semiwiki.com/eda/synopsys/8025-pcie-5-0-jumps-to-the-fore-in-2019/