台积电上周在电话会议上表示,台积电有望在未来几个月内开始大批量生产采用其5nm技术的芯片。虽然到目前为止,与开始生产前几个月的7 nm tape-outs输出相比,5 nm tape-outs输出的数量要少,但TSMC预计该工艺将在商业上取得重大成功。同时,为了确保不受生产限制,该公司计划将2020年的资本支出增加10亿美元。

台积电的N5制造技术比该其N7制造工艺有了实质性的改进(晶体管密度提高了1.8倍,频率增加了15%,功耗则降低了20%),因此公司的主要客户更倾向于N5技术。台积电有望在今年上半年开始使用该技术进行大批量生产(HVM)。到目前为止,与处于相同开发阶段(即HVM之前的几个月)的N7 tape-outs输出数量相比,N5 tape-outs输出数量要少一些,因为alpha客户已经减少了N5设计的数量,而且其他客户尚未赶上。同时,台积电(TSMC)仍对技术的发展持乐观态度,并预计N5收入将占其2020年晶圆销售收入的10%,这意味着N5在其第一年的业务业绩将与N7在其第一年的业绩相同。

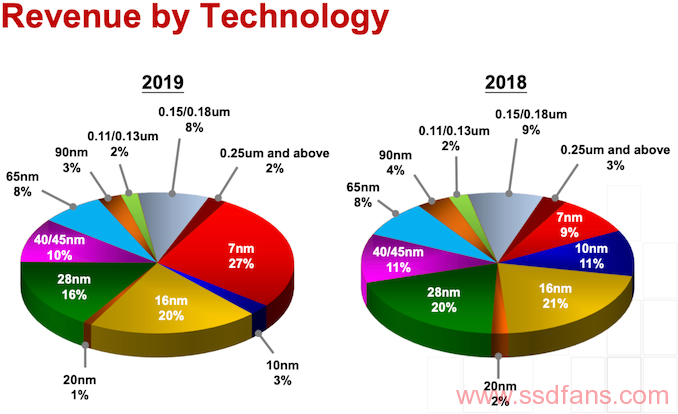

台积电的N7节点之所以取得了巨大的商业成功,原因有很多。首先,它的大多数客户都跳过了10 nm节点,而更积极地选择了7 nm。其次,台积电N7技术没有面临激烈的市场竞争:GlobalFoundries退出了7nm竞赛,而Samsung Foundry几乎没有将其7LPP工艺投入使用。第三,由于N7技术比TSMC的16 nm或10 nm节点复杂得多,因此定价比以前都要高,这为该工艺带来了更大的收益份额。

台积电副董事长兼首席执行官魏建元说:“在同一时期,5 nm的tape-out比7 nm少一点。但是,大批量的tape-out几乎相等。因此,预计5 nm制程将发展非常快速且平稳,它将为今年的收入贡献约10%。”

由于台积电(TSMC)的N7被认为是一个长寿的节点,因此当N5进入HVM时,对该工艺的需求预计不会急剧下降,因为有数十个无晶圆厂半导体开发商正在等待其7 nm工艺投入生产。为了满足使用台积电N7,N7 +,N7P,N6,N5和N5P制造技术制造的芯片的需求,公司将其资本支出增加10亿美元。

台积电并未确切说明这额外的10亿美元将如何使用,但由于在接下来的几个季度中,它将使用极端紫外光刻(EUVL)选择层(在N5情况下最多14层)和其他一些多重图像,铸造厂可能将需要一些额外的前沿设备。

台积电副总裁兼首席财务官黄文德表示:“除了先进技术,我们之前也提到过,今年我们还增加了专用技术和先进包装的资本支出。因此,这些就是我们关注的领域。”