使用专门的硬件来优化传统冯·诺依曼处理器上表现不佳的计算任务,我们称之为“加速”。如今我们已经进入了一个由人工智能技术爆炸驱动的“加速时代”。无数的初创公司致力于开发具有替代架构的芯片,这些架构可以加速和并行化各种类型的计算密集型算法。因此,我们生活在一个异构的计算世界中,处理器和加速器在新一代应用程序中并肩工作。很有可能,这种加速的扩展将包含我们当前的处理概念,而这种异构的方法将仅仅是新的“计算”。

FPGA和SoC FPGA处于这场加速竞赛的前沿和中心。因为每种算法都需要执行于不同的专用硬件架构,所以像ASIC这样的自定义加速器芯片不得不做出妥协,在某种程度上只能充当通用的加速器。从较高层次上看,这意味着系统设计者面临着一个选择,要么是一个具有大量ASIC加速芯片的异构系统来处理各种类型的问题,要么是一个单一类型的折中芯片来处理多种类型的算法。FPGA就是这样一种折中芯片,因为FPGA提供了无限可重构的逻辑,所以我们可以实现每个算法所需的加速器,唯一的折中是在可编程逻辑中实现,而不是固化逻辑。

基于FPGA的加速核心是编程模型。在FPGA结构中实现算法的硬件版本通常需要具有特定FPGA/HDL专业知识的硬件工程师,而且需要大量时间。与传统的软件编程模型相比,FPGA的编程要求要高得多。FPGA行业目前面临的最大挑战是构建一个可行的开发流程,该流程允许使用类似软件的方法来实现FPGA中近乎最优的算法加速。

高层次综合(High-level synthesis, HLS)是一项关键技术,它可以弥补FPGA从算法到体系结构在专业知识和生产效率方面的差距。Xilinx和Intel(两家最大的FPGA公司)都提供针对其FPGA家族的HLS流。这些HLS工具采用C/ C++代码,能够半自动生成硬件设计语言(HDL)体系结构(如寄存器传输级别Verilog),以便在FPGA中实现。

乍一看,我们可能会想“太棒了!问题解决了。”如果能从C/ C++到HDL再到FPGA硬件,我们就能直接编译软件算法,用于实现FPGA加速。但是我们还没有研究细则。

事实证明,HLS工具只能处理非常有限的C/ C++代码,实际上成功地将传统软件引入HLS工具的机率几乎为零。虽然HLS工具可以处理C/ C++,但是为了生成合理的硬件体系结构,需要非常具体的编码风格。有许多数据结构是不可综合的,而获得可综合的代码仅仅是开始。HLS能够为任何特定的算法生成多个体系结构,为了获得满足设计约束的体系结构,您需要硬件设计知识为该工具提供指导。只在HLS工具上抛出一些可综合的C代码,可以很容易地得到一个解决方案,但其性能却比最优解决方案差好几个数量级。

由于这些问题,HLS对于硬件设计人员来说更像是一个强大的工具,而不是一个允许软件设计人员创建硬件的工具。HLS可以极大地提高硬件设计人员的效率,通过掌握HLS,并将C/ C++作为更高级的替代硬件描述语言,硬件(和HLS)专家可以在他们的设计中实现巨大的性能和效率收益。但是这并没有解决我们加速的基本问题——让软件充分利用FPGA加速的优势,而不需要引入一个FPGA专家团队几个月。

这就是Silexica的用武之地。

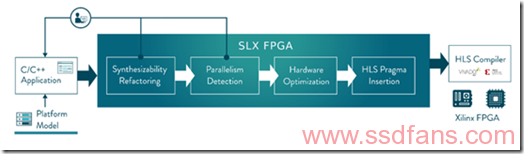

Silexica的SLX FPGA执行静态和动态代码分析,使我们能够深入了解需要加速的C/ C++代码。SLX FPGA识别不可综合的C/ C++代码,检测“硬件”不支持的数据类型,并在FPGA中可加速的C/ C++代码中检测并行性。除此之外,SLX FPGA可以自动或“指导”重构这些代码,以便与HLS一起使用。最后,它会考虑性能目标和可用的FPGA资源(如DSP块和内存),创建优化的HLS实用程序。简而言之,SLX FPGA充当内部的HLS/FPGA专家,将您的算法从“软件”转换为软件和基于FPGA的硬件加速器。

如果在软件代码中有一个循环(或嵌套循环),其中包含一些算术操作,那么通常是展开和/或流水线循环。在循环中经常会有一些很耗资源的计算操作,如乘法累积,可以利用典型FPGA中的DSP资源。FPGA中可能有数千个DSP块,因此在硬件上并行执行数千次的循环迭代在理论上是可行的。并行化的数量和类型取决于FPGA中硬件的可用性和循环结构中的数据依赖性。如一个迭代依赖于前一个迭代的结果,则不能并行执行迭代。

除此之外,大多数算法的软件实现都是用标准的数据类型编写的,很少考虑将其量化到所需的最小位宽。在传统处理器上执行时,这并不重要,因为数据的宽度往往是固定的,而算术处理单元是为这些特定的宽度设计的。然而,在定制FPGA硬件中,可以通过尽可能减少位宽来获得巨大收益,因为这会从加速器架构中移除大量的实际硬件。量化和并行化循环是将软件算法转移到基于FPGA的硬件加速器中最有效的方法。

虽然HLS可以极大地加速创建那些优化的硬件架构,但是它仍然只是轻微地改变了所需的工程技术水平和类型,从“RTL设计人员”到“具有HLS经验的硬件专家”。Silexica SLX FPGA可能不会完全消除对硬件专业知识的需求,但它确实有机会将硬件加速器优化变成更多的“按数字绘图”操作。随着我们看到越来越多的计算密集型任务被转移到使用FPGA加速器的异构计算环境中,了解团队如何利用这种工具将是一件非常有趣的事情。