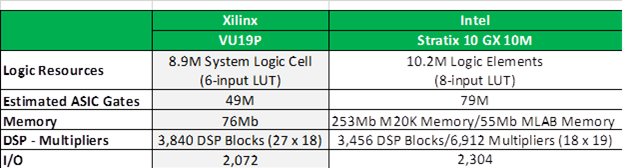

下一代FPGA已经发布,体积明显变大。英特尔即将推出其Stratix 10 GX 10M FPGA,赛灵思已经宣布将于明年秋季正式推出其VU19P FPGA。预计前者将支持约80M ASIC门,而后者将支持约50M ASIC门。为了尽快将这种门容量引入原型实验室,S2C与英特尔合作,推出了新的10M Logic System原型平台,并将在今年年底之前交付首批系统。

使用英特尔新型80M Gate FPGA和S2C进行原型设计

较大的FPGA至少有以下优点:

- 单个FPGA提供更多可用的ASIC门;

- 更高的原型性能;

- 原型制作速度更快。

更多可用的ASIC门

对于那些想从单个FPGA获得更多可用门的人来说,10M逻辑系统是一个可以立即部署的FPGA原型解决方案。在未来几年中,视频处理等领域将需要越来越多的ASIC门。集成了视频模块的SoC已经超过了上一代FPGA的门容量,并且设计人员正在极力跟上当今的视频功能需求,而看不到增加新功能的无限可能。 S2C的10M逻辑系统为现在的视频应用带来了每个FPGA可用门容量的两倍以上,并将于明年年初推出双路和四路FPGA版本支持门容量的持续增长。

更高的原型性能

这些新的,更大的FPGA的另一个优势是性能。S10 GX 10M芯片核心性能额定为900MHz,LVDS I / O和单向I / O分别额定为1.4GHz和250MHz。实际的原型性能会因应用而异,但在所有其他条件相同的情况下进行比较,这些新型14nm FPGA的原型性能将更高。

组织原型设计层次结构时,在一个FPGA中包含高性能块或信号肯定会带来更高的原型性能。借助S2C的新型10M逻辑系统,单个FPGA中可以包含多达8000万门的设计模块;双路和四路FPGA逻辑系统将在FPGA之间包括高速互连。

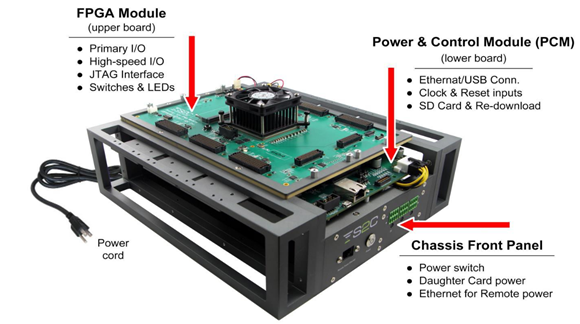

S10 10M逻辑系统支持六个板载可编程时钟(最高350MHz),五个外部时钟和一个振荡器插槽。两个专用的可编程时钟也提供了车载DDR4存储器,可以通过一个车载按钮,一个外部来源的复位通过连接器,或在PlayerPro运行时软件控制。

更快的原型开发

成功进行原型开发的关键之一是最大程度地缩短原型开发时间,并且,快速原型开发必须考虑以下事项:

- 在FPGA原型平台上以目标速度运行设计;

- 一个调试环境,可实现较高的设计可见性和深层的测试响应数据捕获;

- 一种从主机或外部源应用大量高速测试激励的方法。

在FPGA原型平台上以目标速度运行设计应包括为实现FPGA而精心设计的netlist,同时尽可能保持与仿真netlist的相关性。拥有任何具有原型设计经验的原型团队成员将极大地缩短原型开发时间,尤其是在FPGA实现设计时钟和门控时钟、嵌入式存储器和SoC IP方面。

由于仿真netlist是用于硅流片的验证“黄金标准”,因此应将FPGA原型设计视为提高验证覆盖率的一种方法,其范围超出软件仿真的能力。因此,在整个验证过程中保持两个netlist之间的相关性对于总体验证效率至关重要。如果在验证FPGA原型中的设计时出了点问题,就可以通过仿真netlist快速诊断问题的原因,这就是使FPGA原型设计成为如此强大的验证工具的原因。而且,建立并实施严格的bug跟踪和netlist修正规程对于原型生产力的重要性,必须严格强调保持模拟团队与原型团队的同步。

使用S2C的10M逻辑系统进行FPGA原型调试的一种方法是使用S2C的Multi-Debug-Module,即“ MDM”。MDM的设置和运行控件已集成到S2C的PlayerPro软件中,旨在与10M逻辑系统硬件配合使用,并允许在单个窗口中查看来自多个FPGA的测试数据。 MDM最多可提供32K probe,无需重新编译。可以高达80MHz的速度捕获跟踪数据,并且MDM的外部硬件中最多可以存储8GB的波形数据。

S2C Multi-Debug-Module

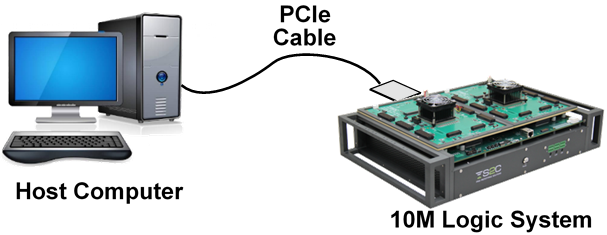

为了帮助缩短原型开发时间,S2C提供了与10M逻辑系统一起使用的ProtoBridge。 ProtoBridge使用原型硬件和主机之间的PCIe或AXI高吞吐量链路,将大量事务级别的测试数据传输给设计。测试数据宽度可以从32位到1024位不等,数据速率高达1GB每秒。

S2C ProtoBridge

原文链接:https://semiwiki.com/semiconductor-manufacturers/intel/279948-webinar-prototyping-with-intels-new-80m-gate-fpga/